# MODELING OF GAN POWER TRANSISTOR PACKAGE FOR DESIGN OF BROADBAND HIGH-POWER AMPLIFIER

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

ÖZLEM BAŞTÜZEL ÇAKMAK

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

ELECTRICAL AND ELECTRONIC ENGINEERING

FEBRUARY 2022

## Approval of the thesis:

# MODELING OF GAN POWER TRANSISTOR PACKAGE FOR DESIGN OF BROADBAND HIGH-POWER AMPLIFIER

submitted by ÖZLEM BAŞTÜZEL ÇAKMAK in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering, Middle East Technical University by,

| Prof. Dr. Halil Kalıpçılar                              |   |

|---------------------------------------------------------|---|

| Dean, Graduate School of Natural and Applied Sciences   |   |

| Prof. Dr. İlkay Ulusoy                                  |   |

| Head of the Department, Electrical and Electronics Eng. |   |

| Dr. Öğr. Üyesi Ahmet Cemal Durgun                       |   |

| Supervisor, Electrical and Electronics Eng., METU       |   |

| Examining Committee Members:                            |   |

| Prof. Dr. Şimşek Demir                                  |   |

| Electrical and Electronics Eng., METU                   |   |

| Dr. Öğr. Üyesi Ahmet Cemal Durgun                       |   |

| Electrical and Electronics Eng., METU                   |   |

| Doç. Dr. Ender Yıldırım                                 |   |

| Mechanical Eng., METU                                   |   |

| Doç. Dr. Lale Alatan                                    |   |

| Electrical and Electronics Eng., METU                   |   |

| Prof. Dr. Özlem Özgün                                   |   |

| Electrical and Electronics Eng., Hacettepe Uni.         |   |

|                                                         | - |

Date: 09.02.2022

| presented in accordance with acad | tion in this document has been obtained and demic rules and ethical conduct. I also declare nd conduct, I have fully cited and referenced ot original to this work. |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |                                                                                                                                                                     |

|                                   | Name Last name: Özlem Baştüzel Çakmak                                                                                                                               |

|                                   | Signature:                                                                                                                                                          |

|                                   |                                                                                                                                                                     |

|                                   |                                                                                                                                                                     |

|                                   |                                                                                                                                                                     |

|                                   |                                                                                                                                                                     |

#### **ABSTRACT**

# MODELING OF GAN POWER TRANSISTOR PACKAGE FOR DESIGN OF BROADBAND HIGH-POWER AMPLIFIER

Baştüzel Çakmak, Özlem Master of Science, Electrical and Electronic Engineering Supervisor: Dr. Ahmet Cemal Durgun

February 2022, 118 pages

Radio frequency (RF) power amplifiers (PAs) are the most crucial part for the development of high performance front-end RF and microwave systems. Power transistor is the key component of a power amplifier, which should be accurately modeled to provide good correlation between simulation and measurement results. Bare die transistor needs to be packaged, before attaching on printed circuit boards (PCBs) to provide protection, easy fabrication and prevent mechanical issues. In recent years, Gallium Nitride (GaN) High Electron Mobility (HEMT) transistors are popular because of high output power, high reliability and high frequency operation capabilities. This thesis reports modeling of an air cavity ceramic package for bare GaN HEMT die transistor to design 0.5-3 GHz broadband PA with 50 W output power and 40 % drain efficiency. For package modeling, two approaches are utilized which are lumped element model based on analytical equations and a numerical model based on full-wave electromagnetic (EM) simulations by Advance Design System (ADS) software. The package and designed PA are fabricated and measured for performance validation. The results show a very good agreement with the simulations, indicating the validity of the modeling methodology.

Keywords: Bare Die Transistor, Air Cavity Ceramic Package, PA, Modeling, GaN HEMT

## GENİŞ BANTLI GÜÇ YÜKSELTEÇ TASARIMI İÇİN YÜKSEK GÜÇLÜ GAN TRANSİSTÖR PAKETİNİN MODELLENMESİ

Baştüzel Çakmak, Özlem Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Tez Yöneticisi: Dr. Ahmet Cemal Durgun

Şubat 2022, 118 sayfa

RF güç yükselteçler, yüksek performanslı aktif RF ve mikrodalga sistemlerinin geliştirilmesinde en önemli parçalardır. Yüksek güçlü amfi tasarımında ölçüm ve simülasyon tutarlılığı açısından, doğru modellenmiş güç transistör kullanmak kritiktir. Çip transistörler, koruma, üretim kolaylığı ve mekanik güç gerekliliği sebepleriyle, baskı devre kartı tasarımlarında paketlenerek kullanılmalıdır. Son yıllarda, yüksek çıkış gücü, yüksek güvenilirlik ve yüksek frekanslarda çalışabilme yetenekleri sayesinde Gallium Nitride (GaN) High Electron Mobility (HEMT) transistörler oldukça popülerdir. Bu tezde, 0.5-3 GHz geniş bandında 50 W çıkış gücü ve 40 % verimlilik sağlayabilen yüksek güçlü amfi tasarımında kullanmak üzere paketlenmiş GaN HEMT çip transistör modellenmiştir. Paket modellemede, ADS kullanılarak simüle edilen 3 boyutlu model ve analitik denklemlere dayanan yığın eleman modeli olmak üzere iki yaklaşım kullanılmıştır. Paket ve tasarlanan amfinin üretimi ve ölçümleri tamamlanmıştır. Simülasyon sonuçları ile modellerin tutarlılığı karşılaştırılmıştır.

Keywords: Çip Transistör, Hava Boşluklu Seramik Paket, Yüksek Güçlü Amfi, Modelleme, GaN HEMT

To my Family...

#### **ACKNOWLEDGEMENTS**

I would like to thank my supervisor Dr. Ahmet Cemal Durgun for his guidance and support. I really appreciate for his encouragements to complete this thesis.

I would also like to thank Ahmet Aktuğ and Ümit İrgin for their support. I learned so much critical information about amplifier design and package modeling from their guidance. I'm grateful to Gökhan Cansız for his encouragement and help during this thesis. I would like to thank Mustafa Kaan Çan for his encouragement for this thesis. I'm also grateful to İlker Comart and Orçun Yıldız for their helps.

I sincerely thank to my husband Mert Çakmak and my family for giving me courage to finalize this thesis.

# TABLE OF CONTENTS

| ABSTRAC   | Tv                                           |

|-----------|----------------------------------------------|

| ÖZ        | vi                                           |

| ACKNOW    | <b>LEDGEMENTS</b> viii                       |

| TABLE O   | F CONTENTSix                                 |

| LIST OF T | TABLES xii                                   |

| LIST OF F | TIGURES xiii                                 |

| 1 INTRO   | ODUCTION1                                    |

| 1.1 Ba    | ackground1                                   |

| 1.1.1     | RF Power Amplifiers                          |

| 1.1.2     | RF Packages                                  |

| 1.2 Ai    | m and Importance of the Study                |

| 1.3 Br    | ief Review on Literature                     |

| 1.4 Ou    | utline and Description of the Thesis9        |

| 2 AIR C   | AVITY CERAMIC PACKAGE MODELING11             |

| 2.1 Ge    | eometry and Structure of Packaged Transistor |

| 2.1.1     | Transistor                                   |

| 2.1.2     | Package Parasitic                            |

| 2.2 Lu    | Imped Element Model of Package               |

| 2.2.1     | Single Bond Wire Model                       |

| 2.2.2     | Mutual Inductance                            |

| 2.2.3     | Lead Model                                   |

| 2.2.4     | Complete Model                               |

| 2.3 3-1   | D Simulation Model of Package29              |

|   | 2.3 | 3.1   | Modeling Strategy                                    | 30   |

|---|-----|-------|------------------------------------------------------|------|

|   | 2.3 | 3.2   | Layout                                               | 33   |

|   | 2.3 | 3.3   | Simulation                                           | 39   |

|   | 2.4 | Cor   | mparison of Models                                   | 40   |

|   | 2.5 | The   | ermal Characterization of Air Cavity Ceramic Package | 43   |

|   | 2.5 | 5.1   | Thermal Model Description                            | 44   |

|   | 2.5 | 5.2   | Calculation and Simulation Comparison                | 44   |

| 3 | PC  | OWE   | R AMPLIFIER DESIGN                                   | 47   |

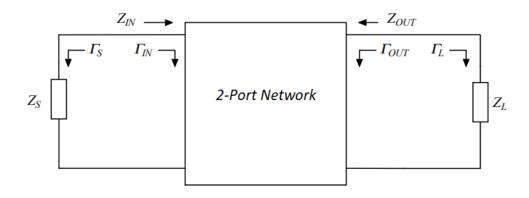

|   | 3.1 | Pov   | wer Amplifier Fundamentals                           | 47   |

|   | 3.  | 1.1   | Bandwidth                                            | 47   |

|   | 3.1 | 1.2   | Power Gain                                           | 48   |

|   | 3.1 | 1.3   | Input and Output Return Loss                         | 49   |

|   | 3.  | 1.4   | Output Power                                         | 50   |

|   | 3.  | 1.5   | Efficiency                                           | 51   |

|   | 3.2 | Des   | sign Procedure                                       | 52   |

|   | 3.2 | 2.1   | Transistor Selection                                 | 53   |

|   | 3.2 | 2.2   | Substrate Material Selection                         | 53   |

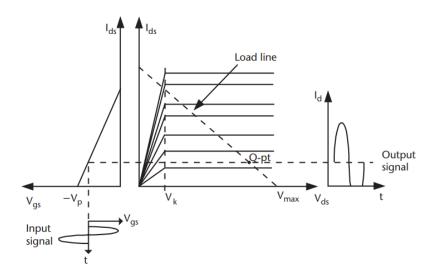

|   | 3.2 | 2.3   | Class of Amplifier                                   | 58   |

|   | 3.2 | 2.4   | Design Methodology                                   | 60   |

|   | 3.3 | Me    | asurement                                            | 81   |

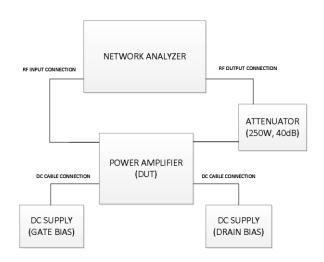

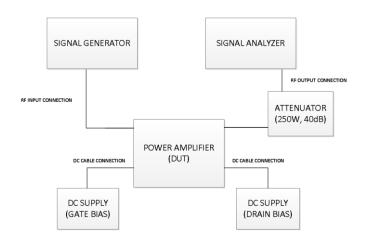

|   | 3.3 | 3.1   | Measurement Setup                                    | 81   |

|   | 3.3 | 3.2   | Measurement Results                                  | 84   |

| 4 | FL  | LIP C | HIP PACKAGE MODELING                                 | 89   |

|   | 4.1 | Flip  | Chip Package Modeling                                | 89   |

|   | 4.2 | Ele   | ctrical Modeling                                     | . 91 |

|    | 4.2.1   | Geometry and Structure of Package Transistor           | 91  |

|----|---------|--------------------------------------------------------|-----|

|    | 4.2.2   | 3-D EM Modeling Methodology                            | 92  |

|    | 4.2.3   | Comparison of Package Models                           | 95  |

| 4  | 4.3 The | ermal Modeling                                         | 98  |

|    | 4.3.1   | Thermal Model Description                              | 99  |

|    | 4.3.2   | Calculation and Simulation Comparison                  | 100 |

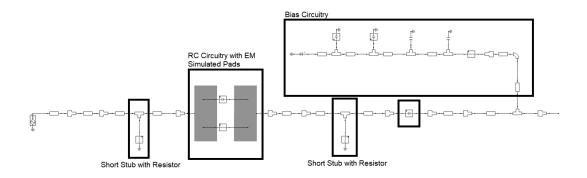

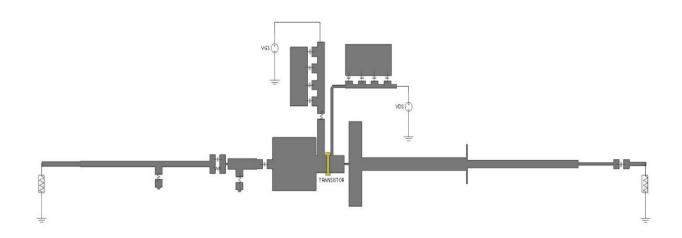

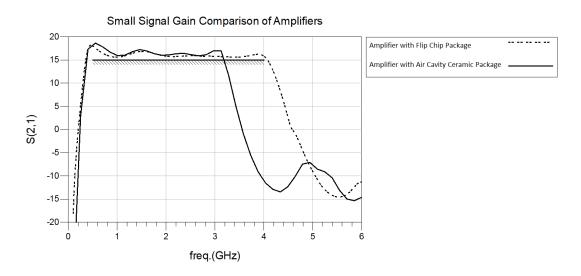

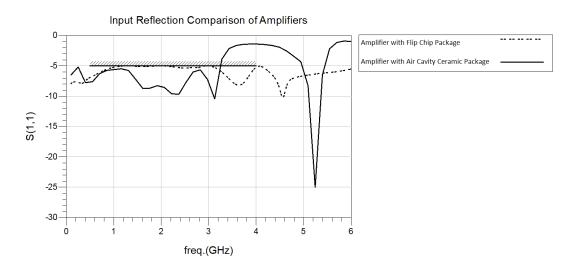

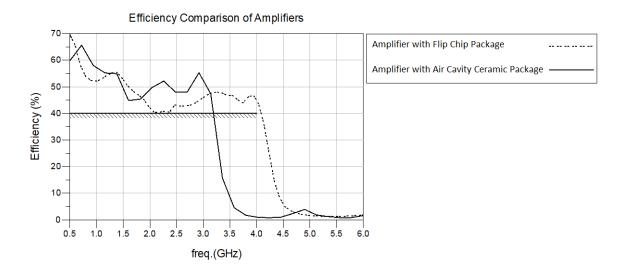

| 4  | 4.4 Am  | aplifier Design and Comparison with Air Cavity Package | 102 |

| 5  | CONC    | LUSION                                                 | 107 |

| RE | FEREN   | CES                                                    | 109 |

| ΑP | PENDIC  | ES                                                     | 115 |

# LIST OF TABLES

| TA | BI | ES |

|----|----|----|

|    |    |    |

| Table 2.1: Geometrical Parameters for Bond Wire Profile                                      |

|----------------------------------------------------------------------------------------------|

| Table 2.2: Properties of Bond Wire                                                           |

| Table 2.3: Analytically Calculated Lumped Element Values of Single Bond Wire22               |

| Table 2.4: Analytically Calculated Lumped Element Values of Single Bond Wire27               |

| Table 2.5: Feed Type versus Calibration used in ADS [21]                                     |

| Table 2.6: Material Properties of Package44                                                  |

| Table 2.7: Thermal Resistance of Layers                                                      |

| Table 2.8: Thermal Resistance of Layers                                                      |

| Table 3.1: Power Amplifier Specifications                                                    |

| Table 3.2: RO6035 Material Properties [28]56                                                 |

| Table 3.3: Comparison of Simulated and Measured Phase Differences58                          |

| Table 3.4: Calculated $\varepsilon eff$ and $D_k$ Values versus Frequency wrt Measured Phase |

| Difference Data                                                                              |

| Table 3.5: Classes of Amplifiers and Characteristics [29]                                    |

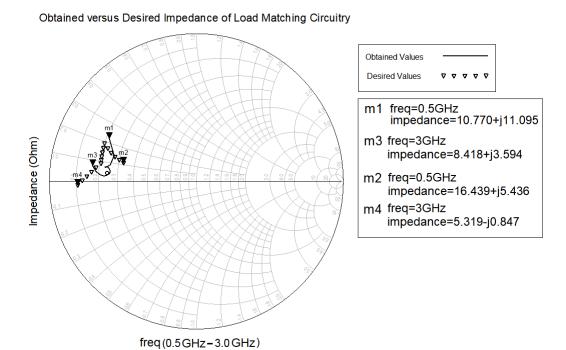

| Table 3.6: Desired Load Matching Impedances with respect to Load Pull Data 74                |

| Table 3.7: Load Matching Circuit Impedance Comparison Graph75                                |

| Table 3.8: Equipment List                                                                    |

| Table 3.9: Obtained and Desired Amplifier Specifications                                     |

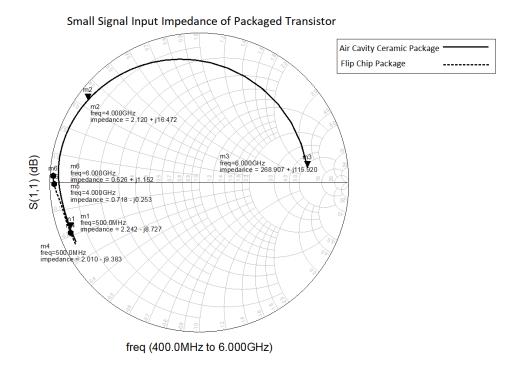

| Table 4.1: Input Impedance Comparison of Package Types95                                     |

| Table 4.2: Material Properties of Flip Chip Package                                          |

| Table 4.3: Thermal Resistance of Layers                                                      |

| Table 4.4: Power Amplifier Specifications                                                    |

# LIST OF FIGURES

| FIGURES                                                                       |     |

|-------------------------------------------------------------------------------|-----|

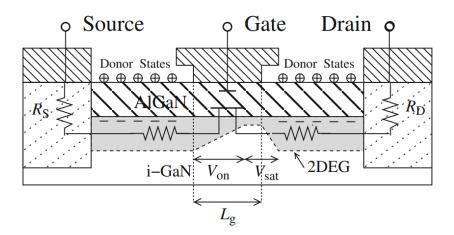

| Figure 1.1: Cross-section of GaN HEMT [1]                                     | 2   |

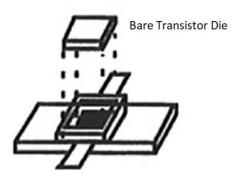

| Figure 1.2: First Level Package Assembly [4]                                  | 4   |

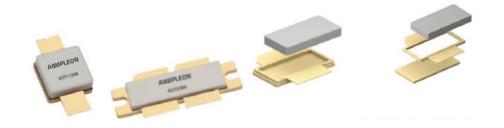

| Figure 1.3: Air-cavity Ceramic Package Examples [4]                           | 5   |

| Figure 1.4: Plastic Package Examples [4]                                      | 5   |

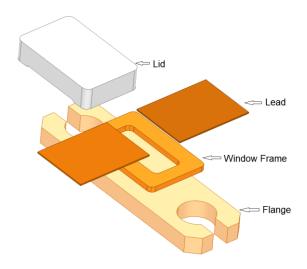

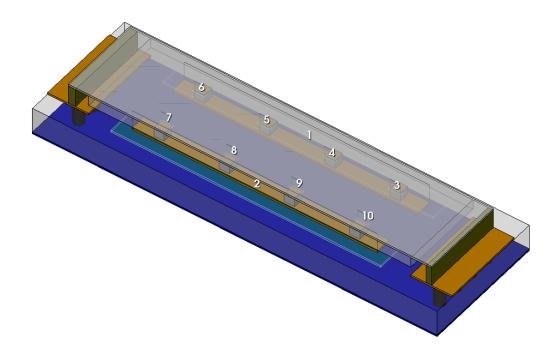

| Figure 2.1: Package Structure                                                 | 11  |

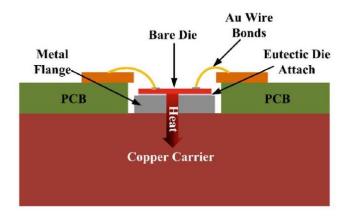

| Figure 2.2: PCB Connection of Packaged Transistor Die [1]                     | .12 |

| Figure 2.3: GaN on SiC HEMT Bare Die [8]                                      | 13  |

| Figure 2.4: Illustration of Packaged Transistor [9]                           | 13  |

| Figure 2.5: GaN HEMT Structure [10]                                           | 14  |

| Figure 2.6: Packaged GaN HEMT Transistor without Lid [11]                     | 14  |

| Figure 2.7: Comparison of Output Power Characteristics of Bare Die Transistor |     |

| and Packaged Transistor [12]                                                  | 15  |

| Figure 2.8: Comparison of Small Signal Gain Graph of Bare Die Transistor and  |     |

| Packaged Transistor [12]                                                      | 15  |

| Figure 2.9: Equivalent Circuit of Input of the Packaged Transistor [12]       | 16  |

| Figure 2.10: Bond wire Equivalent Lumped Element Model                        | 17  |

| Figure 2.11: Bond Wire Profile                                                | 18  |

| Figure 2.12: Skin Depth versus Frequency Graph of Bond Wire                   | 20  |

| Figure 2.13: AC Resistance versus Frequency Graph of Bond Wire                | 21  |

| Figure 2.14: Comparison of Bond wire Length                                   | 22  |

| Figure 2.15: Inductance versus Number of Parallel Bond Wires                  | 23  |

| Figure 2.16: Lumped Element Model of 3 Parallel Bond Wires                    | 23  |

| Figure 2.17: 3 Parallel Bond Wires with and without Mutual Inductance Model   | 24  |

| Figure 2.18: Lead Equivalent Model                                            | 25  |

| Figure 2.19: Skin depth versus Frequency Graph of Lead                        | 27  |

| Figure 2.20: AC Resistance versus Frequency Graph of Lead                     | 28  |

| Figure 2.21: Completed Lumped Element Model of Gate or Drain Side of Packag   | ge  |

|                                                                               | 29  |

| Figure 2.22: EBOND Shape Component                                            | 33  |

| Figure 2.23: EBOND Shape Parameter Window                                         | 34                  |

|-----------------------------------------------------------------------------------|---------------------|

| Figure 2.24: Stack-up of Package                                                  | 35                  |

| Figure 2.25: Lay-out of 3-D Package                                               | 35                  |

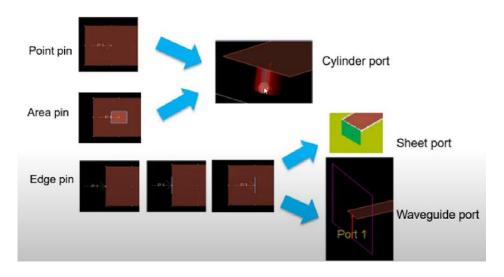

| Figure 2.26: Pin and Port Relation for EM Simulations in ADS [19]                 | 36                  |

| Figure 2.27: External Ports.                                                      | 37                  |

| Figure 2.28: Internal Ports                                                       | 37                  |

| Figure 2.29: Waveguide Port Dimension Guideline [20]                              | 38                  |

| Figure 2.30: Resonance of the Input Circuit of Package in S <sub>11</sub>         | 40                  |

| Figure 2.31: EM Model versus Lumped Element Model S <sub>21</sub> Graph of Single | e Bond              |

| wire Model                                                                        | 41                  |

| Figure 2.32: EM Model versus Lumped Element Model S <sub>21</sub> Graph of Three  | Parallel            |

| Bond wire with Mutual Inductance Between Bond wires                               | 41                  |

| Figure 2.33: EM Model versus Completed Lumped Element Model of Pack               | age S <sub>11</sub> |

| Graph                                                                             | 42                  |

| Figure 2.34: Air Cavity Ceramic Package Thermal Stack-Up                          | 44                  |

| Figure 2.35: Simulation Result of Package                                         | 45                  |

| Figure 3.1: Equivalent Circuit of a Transistor [2]                                | 47                  |

| Figure 3.2: 2-Port Network [23]                                                   | 49                  |

| Figure 3.3: Output Power Degradation with respect to Output Reflection            |                     |

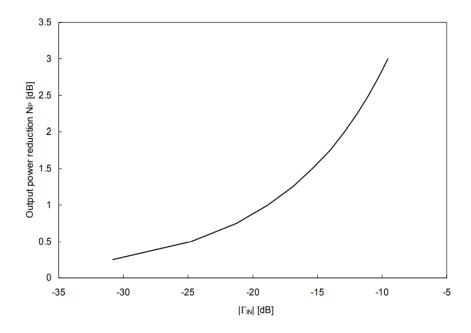

| Coefficient [23]                                                                  | 50                  |

| Figure 3.4: Gain versus Output Power Graph of a Power Amplifier [2]               | 51                  |

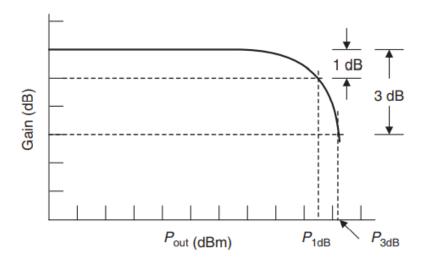

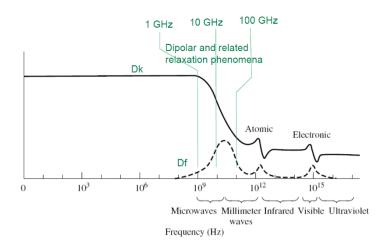

| Figure 3.5: D <sub>k</sub> and D <sub>f</sub> versus Frequency Graph [27]         | 54                  |

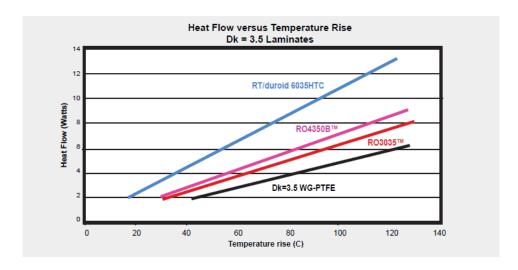

| Figure 3.6: Heat Flow versus Temperature Rise Graph [28]                          |                     |

| Figure 3.7: Class AB Operation Waveform [29]                                      | 59                  |

| Figure 3.8: DC I-V Characteristics with Load Line                                 | 60                  |

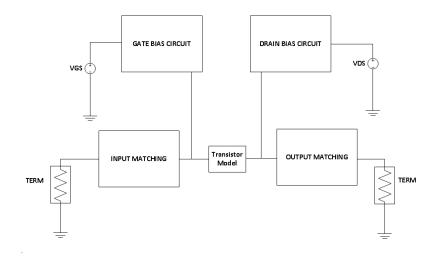

| Figure 3.9: Block Diagram of Power Amplifier Design                               | 62                  |

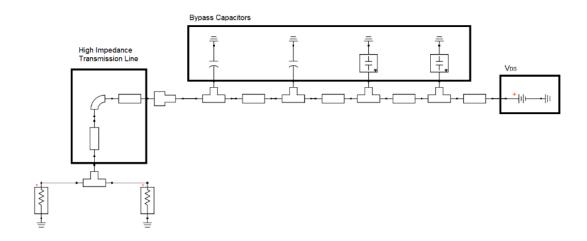

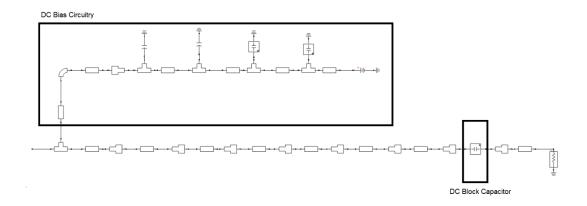

| Figure 3.10: Drain Bias Circuit                                                   | 63                  |

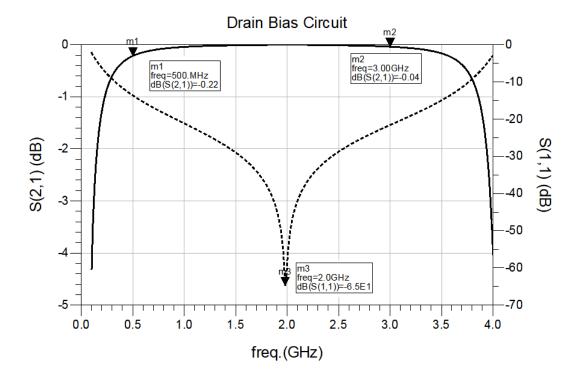

| Figure 3.11: Drain Bias Circuit S <sub>21</sub> and S <sub>11</sub> Graph         | 63                  |

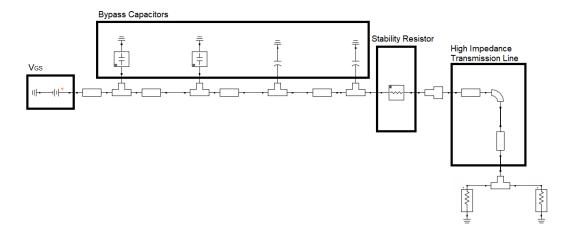

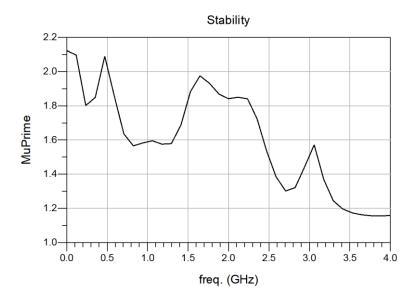

| Figure 3.12: Gate Bias Circuit                                                    | 64                  |

| Figure 3.13: Gate Bias Circuit S <sub>21</sub> and S <sub>11</sub> Graph          | 64                  |

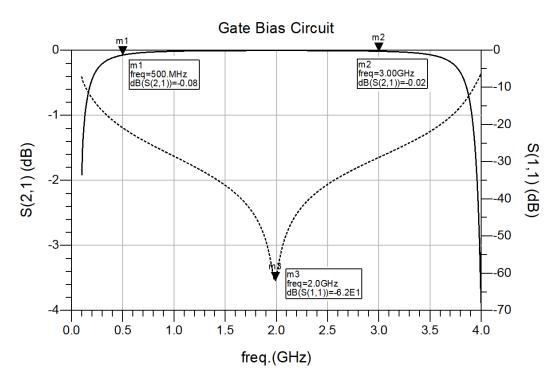

| Figure 3.14: $u'$ Graph of the Design                                             | 66                  |

| Figure 3.15: Input Matching Circuitry                                   | 68   |

|-------------------------------------------------------------------------|------|

| Figure 3.16: Gate Impedances of Transistor Over 0.5-3 GHz Bandwidth     | 68   |

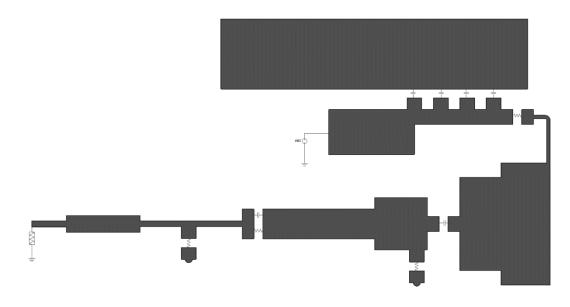

| Figure 3.17: An Example of PCB Lay-out on MoM Solver [32]               | 70   |

| Figure 3.18: Port Feed Types [17]                                       | 70   |

| Figure 3.19:Proper Substrate Definition                                 | 71   |

| Figure 3.20: Input Matching Network Lay-out                             | 71   |

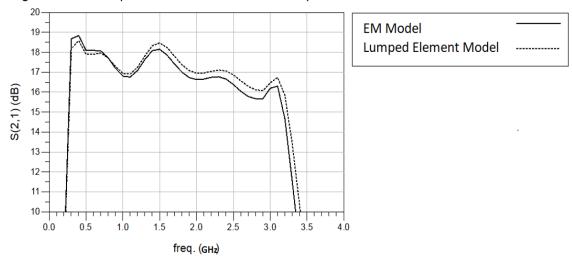

| Figure 3.21: S <sub>21</sub> Graph with Input Prematch and Load Tuner   | 72   |

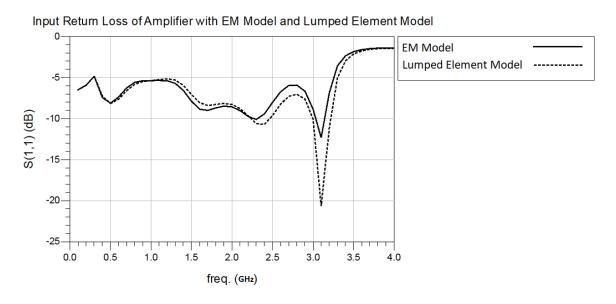

| Figure 3.22: S <sub>11</sub> Graph of Amplifier with Input Prematch     | 72   |

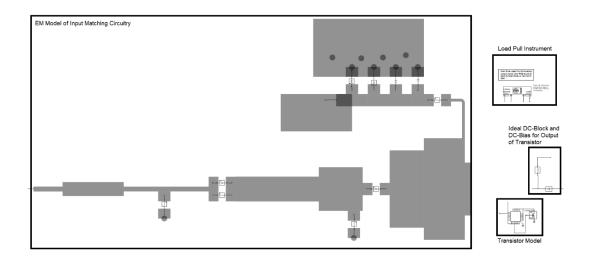

| Figure 3.23: Load Pull Analysis Schematic                               | 73   |

| Figure 3.24: Obtained and Desired Output Matching Impedance Values on S | mith |

| Chart                                                                   | 76   |

| Figure 3.25: Output Matching Circuitry                                  | 76   |

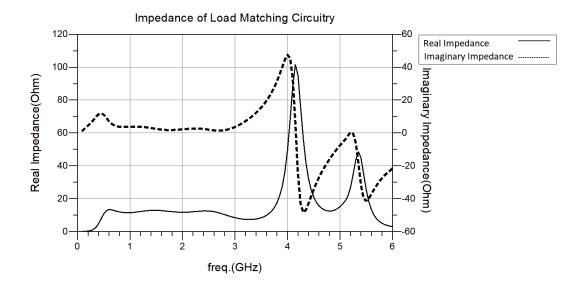

| Figure 3.26: Load Matching Circuitry Impedance                          | 77   |

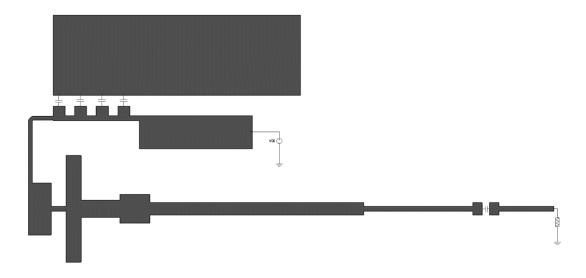

| Figure 3.27:Output Matching Network Lay-out                             | 78   |

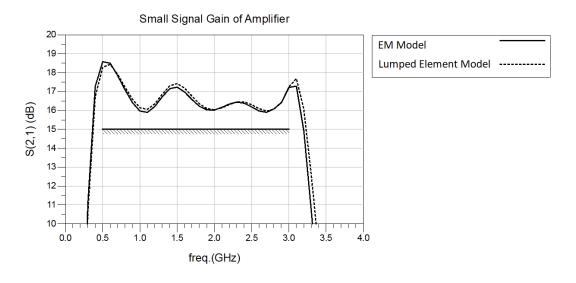

| Figure 3.28: S <sub>21</sub> Graph of Overal Amplifier                  | 78   |

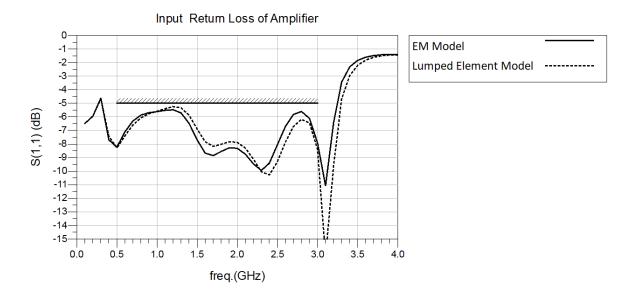

| Figure 3.29: S <sub>11</sub> Graph of Overal Amplifier                  | 79   |

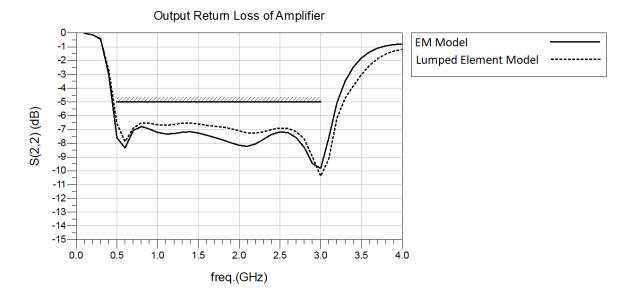

| Figure 3.30: S <sub>22</sub> Graph of Overal Amplifier                  | 79   |

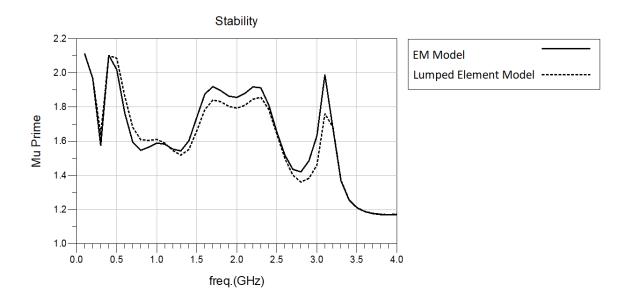

| Figure 3.31: $\mu'$ Graph of Overal Amplifier                           | 80   |

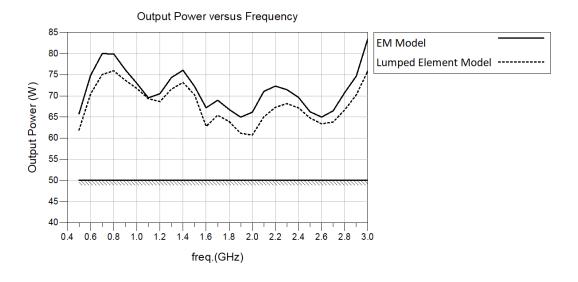

| Figure 3.32: Output Power Graph of Amplifier                            | 80   |

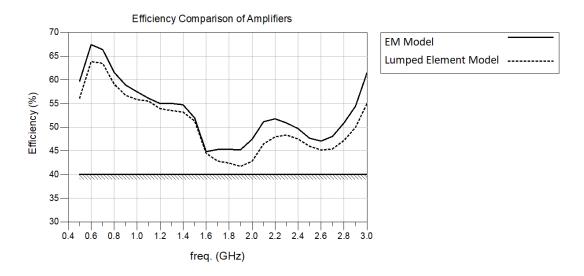

| Figure 3.33: Efficiency Graph of Amplifier                              | 81   |

| Figure 3.34: Small Signal S-parameter Measurement Setup                 | 82   |

| Figure 3.35:Large Signal Measurement Setup                              | 83   |

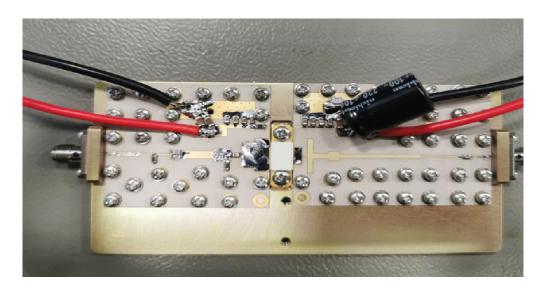

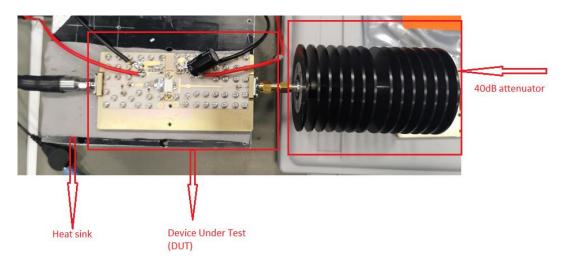

| Figure 3.36: Power Amplifier (DUT)                                      | 83   |

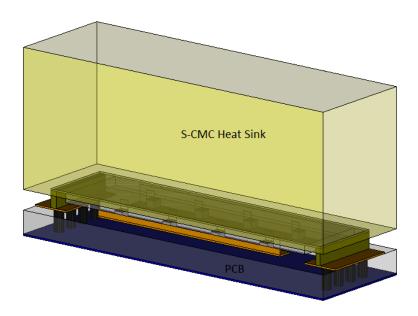

| Figure 3.37:DUT, Heat Sink and 40 dB Attenuator                         | 84   |

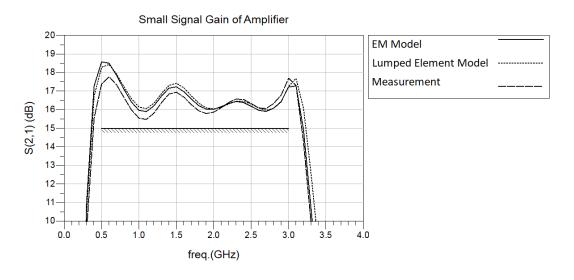

| Figure 3.38: S <sub>21</sub> Graph                                      | 84   |

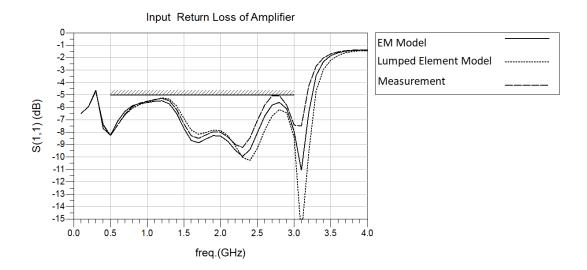

| Figure 3.39: S <sub>11</sub> Graph                                      | 85   |

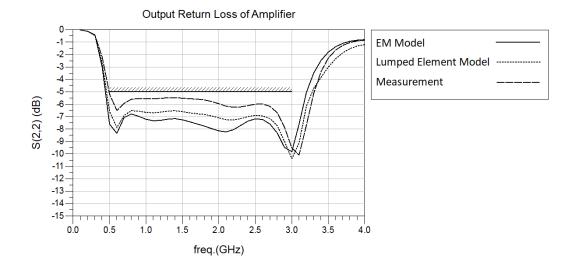

| Figure 3.40: S <sub>22</sub> Graph                                      | 85   |

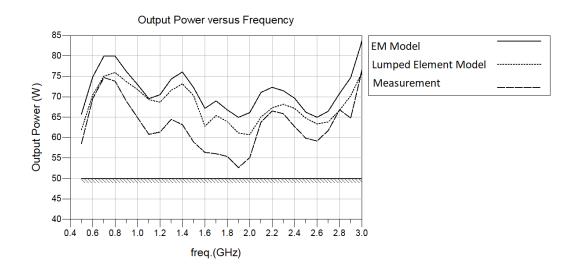

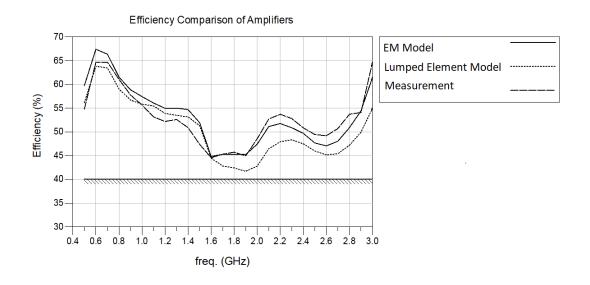

| Figure 3.41: Output Power versus Frequency                              | 86   |

| Figure 3.42: Efficiency versus Frequency                                |      |

| Figure 4.1: General Flip Chip Topology [36]                             |      |

| Figure 4.2: 3-D Model of Flip Chip Package                              | 91   |

| Figure 4.3: Defined Stack-up of Flip Chip Package93                              |

|----------------------------------------------------------------------------------|

| Figure 4.4: Assigned Ports94                                                     |

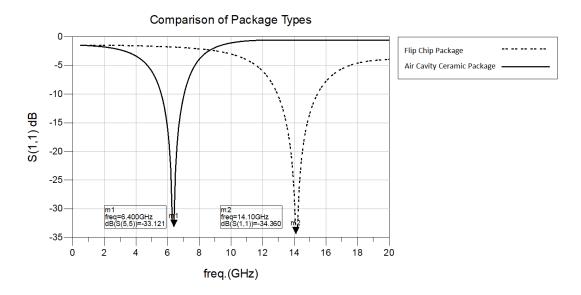

| Figure 4.5: Comparison of Resonant Frequencies of Packages Types95               |

| Figure 4.6: Comparison of Input Impedances of Package Types96                    |

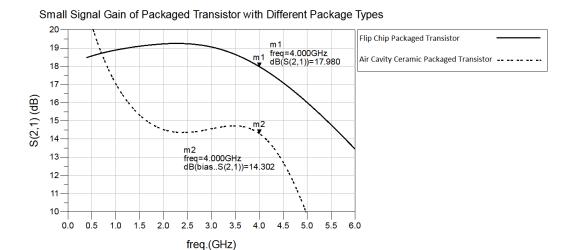

| Figure 4.7: Comparison of Small Signal Gain of Packaged Transistors at 4 GHz .97 |

| Figure 4.8: Comparison of Output Power of Packaged Transistors at 4 GHz97        |

| Figure 4.9: Comparison of Output Power of Packaged Transistors at 6 GHz98        |

| Figure 4.10: Comparison of Small Signal Gain of Packaged Transistors at 6 GHz98  |

| Figure 4.11 : Flip Chip Package Thermal Stack-Up99                               |

| Figure 4.12: Simulation Result of Package                                        |

| Figure 4.13 : EM Simulated Lay-out of Designed Amplifier with Flip Chip          |

| Packaged Transistor                                                              |

| Figure 4.14:Small Signal Gain Comparison of Amplifiers with Different Packaged   |

| Transistor                                                                       |

| Figure 4.15: Input Return Loss Comparison of Amplifiers with Different Packaged  |

| Transistor                                                                       |

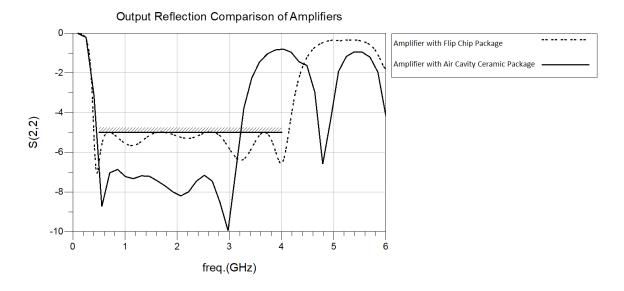

| Figure 4.16: Output Return Loss Comparison of Amplifiers with Different          |

| Packaged Transistor                                                              |

| Packaged Transistor 104                                                          |

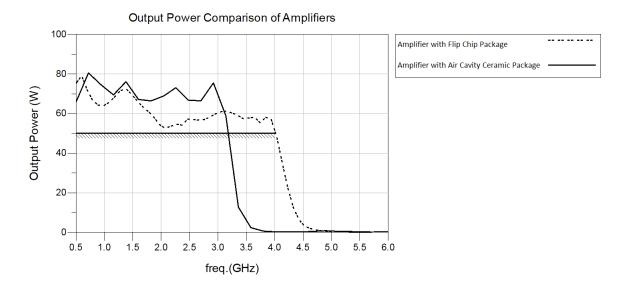

| Figure 4.17: Output Power Comparison of Amplifiers with Different Packaged       |

| -                                                                                |

| Figure 4.17: Output Power Comparison of Amplifiers with Different Packaged       |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Background

#### 1.1.1 RF Power Amplifiers

RF PA is a critical component of transmitters which amplify the power of signal being transmitted [1]. PAs operate in nonlinear large signal operation region, which results in distortion of the signal reducing the efficiency of transmission. Furthermore, efficiency should be high to prevent power dissipation. To maximize efficiency, harmonic terminations may be presented to the output of the transistor [1]. Also, because of the need for high-speed wireless transmitters, the bandwidth of PAs should be enhanced. To design a broadband PA, design architectures should be modified which is very challenging.

RF PAs have following characteristics as given below [2];

- RF response with a limited band

- Direct current (DC) to RF conversion efficiency of less than 100 %

- RF coupled response with no DC

- Nonlinearity which results in mixing products from numerous signals

- Phase difference between the input and output

- Higher gain at low temperatures, in other words, temperature dependent gain

- Power dependent amplitude

It is possible to divide the history of PAs in three eras [3]. First one is the era of waveguides and microwave vacuum tubes that extend over 10 GHz in terms of practical devices. The second era of PAs is a longtime period which is through 1960s

until the end of the 1980s [3]. Major new developments such as reduction in size, which is achieved by using integrated circuits, are achieved in this term. During this era, many of the military systems are developed by using chip components, which are attached to the ceramic substrates. Today, this technology is known as Microwave Integrated Circuit Technology (MIC), which is still an integral part of microwave components in the high frequency band [3]. The third era of PA technology is wireless communications which can be characterized by low cost and high-volume complex systems. More functional chips and high frequency packaging advances are observed. Broadband techniques are placed aside, because all military systems are inherently broadband.

The first one of the two of leading field effect transistors (FETs) is lightly doped metal-oxide semiconductor (LDMOS), which is a low-cost transistor used below 3 GHz applications [1]. The second one is the GaN HEMT, whose operating frequency reaches up to mm-waves because of its high electron mobility feature. Drain voltages of both technologies are very large up to 60 V, which provides high output power levels [1]. For GaN devices, drain voltage up to 90 V is also possible [1].

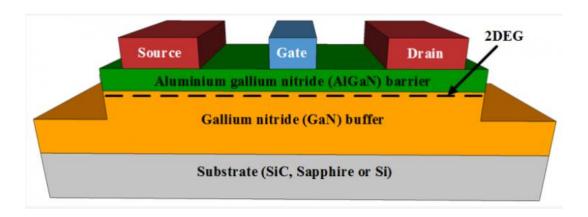

GaN HEMT structure is given in Figure 1.1, which shows source to drain cross-section of a single finger of die transistor.

Figure 1.1: Cross-section of GaN HEMT [1]

Source and drain electrodes are placed at the top of the Aluminium Gallium Nitride (AlGaN) layer, which creates an ohmic contact with 2-Dimensional Electron Gas (2DEG). AlGaN layer presents wide bandgap which acts as an insulator for field effect transistor. Short circuit is created between source and drain electrodes until 2DEG pool of electrons is depleted and GaN crystal blocks the current flow. In order to deplete 2DEG pool of electrons, the gate electrode is placed on the AlGaN layer. By applying a negative voltage to the gate electrode relative to the drain and source, device can be turned off. This is why the device is named as depletion mode transistor. Thus, a negative voltage must be applied to the gate of the transistor in order to prevent short circuit [4]. Because the channel is undoped, electrons in 2DEG region present high mobility which is the reason that FET is calling as HEMT.

#### 1.1.2 RF Packages

RF packages are commonly used for telecommunication and military applications [4]. In general, transistors are placed in low-cost plastic packages for commercial applications. However, for military applications, custom packages are designed in order to obtain higher performance and reliability [4]. With respect to modeling methods, operating frequency band and cost, RF packaging technologies are quickly growing up.

Selecting an appropriate package and assembly technique has an important effect on performance, reliability and cost of a transistor. Effects of assembly techniques and package parasitic should be minimized during packaging process in order to prevent performance degradation of transistor. Also, package complexity should be considered to minimize the cost.

Most commonly used packaging method is first level package assembly which means transistor is placed in individual package as seen in Figure 1.2 [4]. First level package assembly includes die bonding and wire bonding. The most critical challenge in first level package assembly is to prevent effect of assembly on performance of RF component. The most important parameters that should be taken

into consideration are bond wire dimension, lead dimension, grounding effect of leads and thermal effect of package materials to keep temperature of transistor in the safe zone.

Figure 1.2: First Level Package Assembly [4]

Specifications of the packaging depend on application. For example, in communication applications below 18 GHz and low power operations, Gallium Arsenide (GaAs) technology transistors are housed in plastic packages to decrease the cost. However, for high power, high frequency and high performance requirements, ceramic packages with metal base are required because of low thermal resistance, high power capability and better reliability [4].

#### 1.1.2.1 Types of RF Packages

RF packages can be classified according to their material, which are determined with respect to operating frequency, thermal reliability, cost, dissipated power and etc. The basic package types are ceramic and plastic packages.

#### 1.1.2.1.1 Ceramic Packages

Ceramic packages comprise of a ceramic material as a base material under the leads, in order to provide high isolation and lower loss [4]. Bare die transistor is placed in an air cavity with a ceramic or metal lid on the top. Die is generally soldered on the metal base to provide heat transfer from the package. For high power applications,

metal base which is named as flange is directly attached to the heat sink. Depending on the environmental requirements, packages can be hermetic or non-hermetic. The ceramic packages can be surface mounted on PCB or soldered on modules. Different examples of air-cavity ceramic packages are shown in Figure 1.3 [4].

Figure 1.3: Air-cavity Ceramic Package Examples [4]

#### 1.1.2.1.2 Plastic Packages

Plastic packages are generally covered with plastic molding compound, no lid is involved and there is no air cavity [4]. The molding compound has an impact on the operating frequency of the transistor at high frequencies. Because of material properties of plastic, isolation between the leads of the plastic packages is lower. Also, plastic packages are non-hermetic. Although plastic packages have lower isolation and operating frequency, they are more suitable for high volume manufacturing because of their low cost.

The lead frame is the supporting structure for die attach in the plastic packages. The lead frame is sealed from a thin metal. Die is attached on the lead frame with electrically conductive epoxy. Examples of plastic packages are given in Figure 1.4 [4].

Figure 1.4: Plastic Package Examples [4]

#### 1.1.2.2 Materials for RF Packages

Types of materials used in the RF packages are given in this part.

#### **1.1.2.2.1 Ceramics**

Substrate materials of ceramic packages are generally alumina (Al<sub>2</sub>O<sub>3</sub>), aluminum nitride (AlN), beryllium oxide (BeO), glass (SiO), glass alumina (LTCC) or silicon carbide (SiC) [4]. Al<sub>2</sub>O<sub>3</sub> is the most popular substrate material between them. High melting point and chemical stability are the most important features of ceramic materials. Furthermore, electrical, thermal and mechanical properties of ceramic materials are perfectly combined.

#### 1.1.2.2.2 Metals

The most popular lead material of ceramic packages is kovar [4]. Kovar has good thermal expansion coefficient (CTE) match with ceramics. In contrast to all good specifications, kovar has poor thermal conductivity. Thus, kovar is used at package leads in high power applications and as a flange in low power applications. The preferred flange material for high power applications is generally CuW or CMC (Cu-Mo-Cu) because of good thermal conductivity [4].

### 1.2 Aim and Importance of the Study

High power transistors should be packaged in order to keep junction temperature low and steady and improve heat sinking capability [4]. Furthermore, thermal consideration prevents performance degradation of transistor and provides high reliability and durability. High power transistor packages require thermal interface materials, heat spreaders and bonding materials. The source of the bare die transistor is directly attached to the ground with back-vias, in order to provide low thermal resistivity [1].

Moreover, high power transistors should be packaged to protect bare die transistor from environmental conditions, make circuit fabrication easier and provide mechanical strength in PCB applications.

Contrary to all these functional advantages of transistor packages, package parasitic degrade the performance of bare die transistors [1]. Because of parasitic of package, operating frequency of transistor decreases. Also, gain and output power degradation are observed. Therefore, dimension and materials of packages should be determined to decrease parasitic effects as much as possible. However, there are some difficulties. High power bare die transistor size is the first factor to determine package size, because the bond wire shape should be identical all around the die to provide equal current distribution. The other and the most important limiting factor is the manufacturing capabilities. Distance between bond wires, dimension of bond wire, material mismatches and cost, should be considered during the package design. In this work, specifications of all components of the package are determined to decrease parasitic effects without disturbing manufacturing tolerances.

One of the most critical point in this work is the accurate modeling of the package. Since the parasitic degrade the performance of transistor, it should be determined accurately to estimate the performance of packaged transistor correctly. In order to validate a PA design, packaged transistor model should be accurate to obtain a good agreement between simulation and test results. Because it is not straightforward to measure the response of a package, a modeling approach should be utilized to obtain the behavior of the package. In addition, because response of package is not provided by any manufacturer, the only way is modeling of the package.

Furthermore, because procurement of high-power packaged transistor is not easy, there is a need to model and manufacture package and embed the die transistor in it to use in high PA design.

In this work, two different approaches are presented. The first one is the lumped element model which replaces the package parts such as bond wires, gate and drain leads by their lumped element representations, whose values are obtained by analytical equations. The importance of suggested lumped element model of the package is that there is no need to use a 3-D EM simulation tool. Also, it is possible to create model easier, quicker and cheaper than the simulation tools. The second approach is the 3-D EM model of the package which is created by using ADS EM simulation software.

The last critical part of this work is the design of a broadband high PA, by using the package model with the nonlinear bare die transistor model. The designed PA is manufactured, tested and results are compared with simulations. Suggested lumped element and EM models of the package are verified.

The main contributions of this work can be summarized as below;

- Two modeling methodologies are developed for accurate model of power transistor package.

- The first in-house power transistor package is manufactured, by utilizing the developed modeling methodologies.

- The manufactured package is used in the design of a 0.5-3 GHz broadband 50 W high PA.

- The designed power amplifier is manufactured and tested.

- The validity of the lumped element and full-wave EM package models are verified by comparing simulations and measurement results.

- As a future work, a package model is suggested. This model is designed to eliminate package parasitic and increase operation frequency of PA design.

#### 1.3 Brief Review on Literature

For package modeling, almost always, full-wave EM simulation methodologies are used [5]. Although the most reliable way to obtain response of the package is 3-D EM simulation, it is a complex and long-time process. Also, high computing power and memory are needed. Furthermore, there is a need of EM simulation software which is expensive. To provide numerical robustness and increase convergence speed, a distributed model is provided [6]. By using S-parameter matrix which is

obtained by using EM simulation software, lumped element values are estimated at 2 GHz [6]. However, the accuracy of this extraction method is not enough to estimate the resonant frequency of package at high frequencies. Thus, the lumped element model methodology is suggested in this work, which is based on generation of the equivalent circuit and calculation of lumped element values of each part of the package analytically. Suggested methodology is more accurate and eliminates the need of 3-D EM simulation software.

#### 1.4 Outline and Description of the Thesis

This work comprises of three parts, modeling of the GaN power transistor package with two different approaches, design of a broadband high PA and suggestion of a packaging strategy for performance improvement.

In Chapter 2, package geometry and structure of packaged transistor are described and effects of package parasitic are mentioned. Generation of first modeling method which is lumped element model is described step by step. Analytical formulations of lumped element values of package are determined and completed model of package is obtained. As a second approach, 3-D EM model of the package which is obtained by using ADS is presented. 3-D EM simulation process is started by generating 3-D lay-out of package which comprises of creating bond wire profile, defining stack-up, assigning ports and simulation, respectively. Modeling strategy and simulation results are examined. As a last, 2 different modeling approaches are compared and discussed shortly. Nonlinear model of the transistor which is provided by the manufacturer and the package model in this work are combined. Packaged transistor model is obtained in order to be used in the PA design in Chapter 3. At the end of the chapter, thermal characterization of the packaged transistor is performed and a thermal model is created.

In Chapter 3, PA design fundamentals and design procedure are described step by step. In order to test the modeled and fabricated package performance, broadband, high PA is designed. All simulations are performed with the packaged transistor

models of Chapter 2. Broadband high PA with embedded produced packaged transistor is measured and simulation results are compared at the end of the chapter.

In chapter 4, a new package is suggested as future work. First, electrical model of package is created by using simulation software. Then, thermal model of package is created. At the end of the chapter, contributions of the suggested package are described and compared with air cavity ceramic package.

#### **CHAPTER 2**

#### AIR CAVITY CERAMIC PACKAGE MODELING

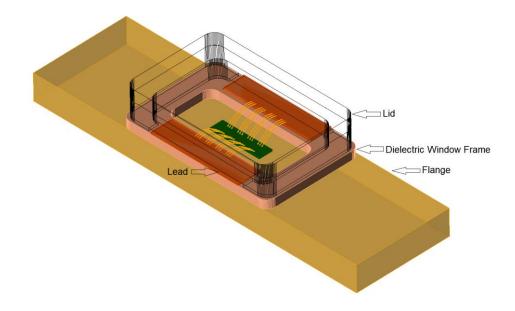

#### 2.1 Geometry and Structure of Packaged Transistor

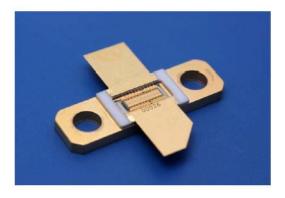

High power transistors are generally placed in air cavity ceramic package [1]. An air cavity ceramic package includes a metal flange, a dielectric window frame, gate and drain leads and a lid as seen in Figure 2.1.

Figure 2.1: Package Structure

Metal flange material is chosen as S-CMC (Cu:Mo:Cu:Mo:Cu) because of good thermal specifications [1]. This material provides low thermal resistance and good CTE match with the active device. Standard metal flange dimension is preferred in order to decrease manufacturing cost. For mounting purpose, there are two holes in the flange, which behaves as a heat sink for the power transistor. A dielectric window frame is mounted on the flange which is chosen as Al<sub>2</sub>O<sub>3</sub>, because of high temperature stability and low CTE specifications [4]. Leads are mounted onto the

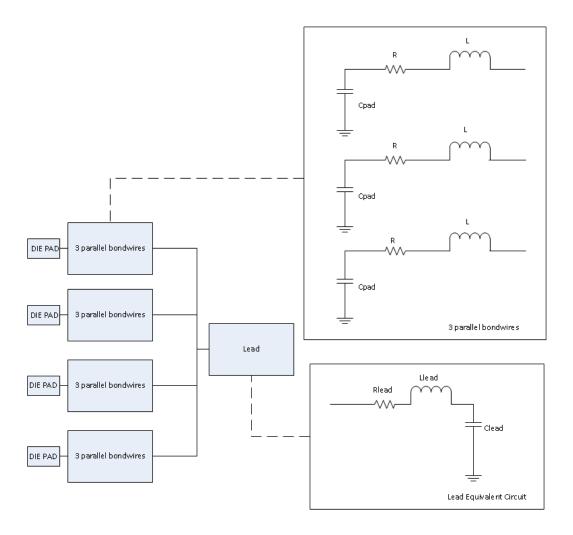

dielectric window frame which provides connection between gate and drain pads of the die and the PCB through bond wires, as seen in Figure 2.2 [1]. Material of leads are chosen as kovar, because of good CTE match with Al<sub>2</sub>O<sub>3</sub> [4]. The bare die transistor is attached to the flange by using eutectic soldering. There are three gold 1-mil-diameter bond wires connected at each gate and drain pad of the bare die transistor. The distance between the bond wires is kept constant while considering manufacturing limits. The lid which is manufactured with epoxy on it is glued on the top of the package.

Figure 2.2: PCB Connection of Packaged Transistor Die [1]

Source of the bare die transistor is directly connected to the flange with back vias, in order to provide good mechanical contact with low thermal resistivity. To reduce the thermal resistance and provide strong physical contact between flange and heat sink carrier, generally, a gap filler material is inserted between them [1].

#### 2.1.1 Transistor

In this work, GaN HEMT bare die transistor is chosen as an active device. GaN technology has prominent properties which are large bandgap, high breakdown voltage, high electron velocity and high thermal conductivity [7]. Thanks to high breakdown voltage capability, high drain voltage can be applied to the drain of the transistor and higher output power level can be obtained. Because of high electron

velocity feature, high frequencies can be reached. By means of high thermal conductivity, high temperature can be tolerated [7].

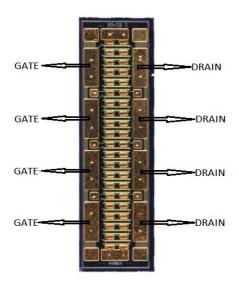

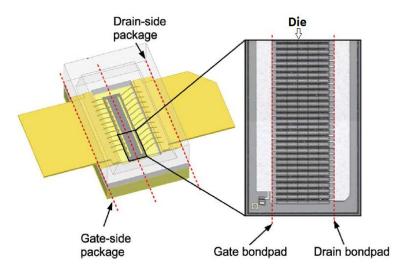

Bare die transistor consists of power unit cells which include gate, drain and source pads as seen in Figure 2.3 [8]. Source pads are grounded with back vias, thus transistor is used as common source transistor model. Gate DC biasing and RF feeding is done through gate pads. Drain DC biasing circuitry and RF output matching network are connected to drain pads as seen in Figure 2.4.

Figure 2.3: GaN on SiC HEMT Bare Die [8]

Figure 2.4: Illustration of Packaged Transistor [9]

The basic GaN HEMT structure which includes gate, source and drain electrodes is shown in Figure 2.5 [10].

Figure 2.5: GaN HEMT Structure [10]

#### 2.1.2 Package Parasitic

Power transistor package has important functions such as protecting bare die transistor from environmental conditions, making circuit fabrication easier, improving heat sinking capability and providing mechanical strength [11]. Besides all these functionalities, package affects the electrical performance of transistor [11].

Figure 2.6: Packaged GaN HEMT Transistor without Lid [11]

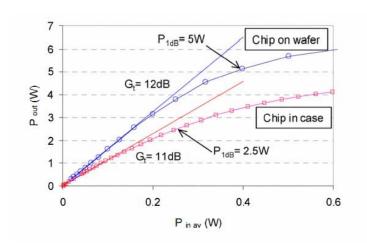

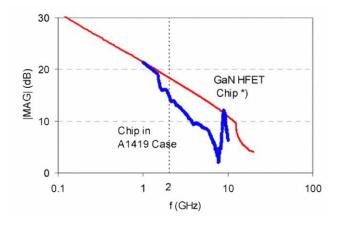

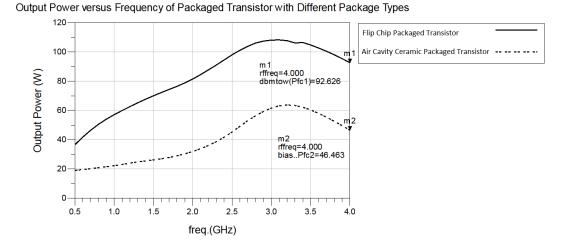

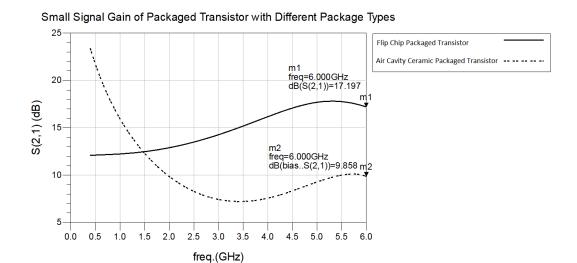

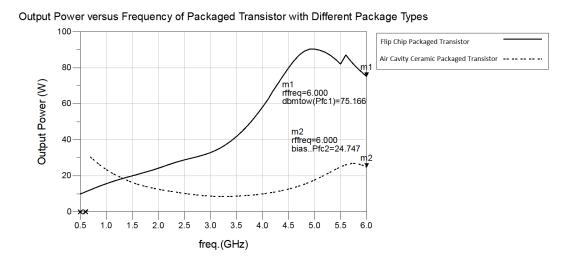

Packaged transistor has generally degraded performance with respect to bare die transistor as shown in Figure 2.7 which illustrates large signal performance of both chip on wafer and chip in case. Same degradation is valid for small signal performance of the transistor as shown in Figure 2.8 [12]. At high frequencies, small signal gain degradation is obvious. Because of package resonance, usable frequency range reduces [12].

Figure 2.7: Comparison of Output Power Characteristics of Bare Die Transistor and Packaged Transistor [12]

Figure 2.8: Comparison of Small Signal Gain Graph of Bare Die Transistor and Packaged Transistor [12]

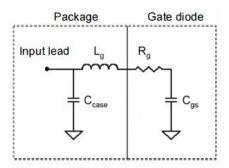

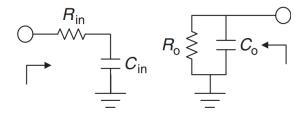

Package effects are mainly due to bond wire inductances, mutual coupling between bond wires, lead capacitances and coupling between the input and the output of the package [12]. The inductance and capacitance provided by the package result in resonances, which are critical for high frequency applications [12]. Resonance occurs due to large physical dimensions of the package. For wideband transistors, resonance is critical [12]. At the input of the transistor, lead capacitance and inductance of bond wires create a resonance. The simple equivalent circuit of input of the packaged device is depicted in Figure 2.9 [12]. These effects should be carefully modeled in order to predict electrical performance of the packaged transistor accurately [6].

Figure 2.9: Equivalent Circuit of Input of the Packaged Transistor [12]

In this work, two different modeling approaches are discussed and compared. The first approach is the equivalent lumped element model based on analytical calculations of package parasitic. The second approach is based on 3-D EM simulation model.

#### 2.2 Lumped Element Model of Package

Lumped element model is the simplest way to predict the impact of package on electrical behaviour of the die transistor [5]. Bond wire inductances, mutual coupling between parallel bond wires and lead capacitances can be calculated analytically. Lumped element models can be used to increase simulation speed and increase numerical convergence even at higher frequencies with some extentions [5]. Even though, calculating the coupling between gate and drain side bond wires is not

possible with lumped element modeling method, it can be ignored in this work because of low operating frequency range.

The development of the analytical model consists of multiple steps. First, a single bond wire is modeled. Then, the mutual inductances between the neighboring bond wires are included. Finally, the leads are modeled and lumped element values are calculated. The final analytical model is compared with 3-D EM simulation model.

#### 2.2.1 Single Bond Wire Model

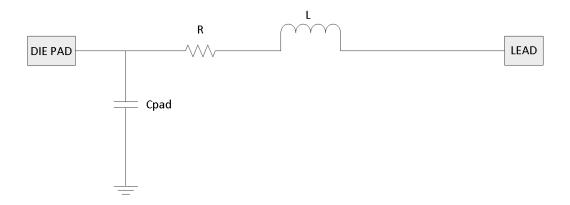

Bond wires are represented as a self inductance and series resistance as shown in Figure 2.10 [13]. Capacitance of the landing pad of the bond wire should be added to the model.

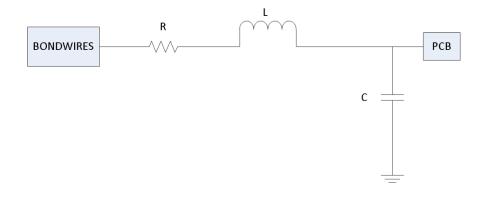

Figure 2.10: Bond wire Equivalent Lumped Element Model

For a bond wire with length l and radius r parallel to a ground plane, self inductance calculation can be written as Equation (2.1) where h is the distance between ground plane and the conductor [13].

$$L = \frac{\mu_0 \mu_r}{2\pi} \ln\left(\frac{2h}{r}\right) l \tag{2.1}$$

The relative permeability  $\mu_r$  can be taken as 1 for a nonmagnetic substrate and  $\mu_0$  is the permeability in a vacuum  $(4\pi \times 10^{-7} \text{ H/m})$ .

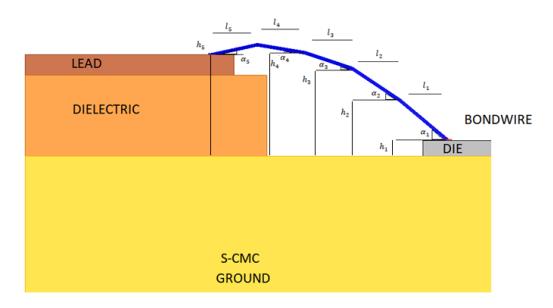

The inductance of bond wire depends on its profile, which is shaped by dividing it in 5 smaller pieces to obtain producible and real-like bond wire as shown in Figure 2.11. Contributions of all parts of the bond wire can be calculated separately and summed to obtain the total inductance. The inductances of all 5 pieces of the bond wire profile can be calculated by using Equation (2.2), where  $\alpha$  is angle between ground plane and piece of bond wire as seen in Figure 2.11.

$$L_{i} = \frac{\mu_{0}}{2\pi} \int_{0}^{l_{i} \sec{(\alpha_{i})}} \ln{\left[\frac{2(l \sin(\alpha_{i}) + h_{i})}{r}\right]} dl \qquad where \ i = 1,2,3,4,5$$

(2.2)

Calculated inductance values by using Equation (2.2) are given in Table 2.1, together with the associated geometrical parameters.

Figure 2.11: Bond Wire Profile

Table 2.1: Geometrical Parameters for Bond Wire Profile

| Height | (µm) | Length  | (µm) | Angle      | (°)   | Inductance | (nH)  |

|--------|------|---------|------|------------|-------|------------|-------|

| $h_1$  | 100  | $l_{1}$ | 300  | $\alpha_1$ | 39.80 | $L_1$      | 0.275 |

| $h_2$  | 350  | $l_2$   | 300  | $\alpha_2$ | 33.69 | $L_2$      | 0.307 |

| $h_3$  | 550  | l 3     | 300  | $\alpha_3$ | 18.43 | $L_3$      | 0.288 |

| $h_4$  | 650  | $l_{4}$ | 300  | $lpha_4$   | 9.46  | $L_4$      | 0.284 |

| $h_5$  | 640  | $l_{5}$ | 300  | $\alpha_5$ | 12.24 | $L_5$      | 0.287 |

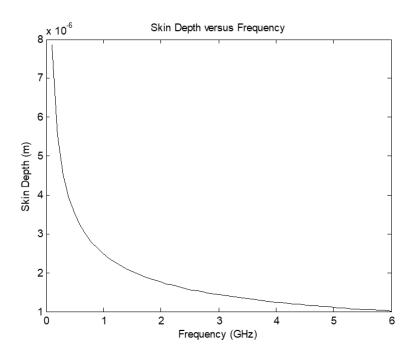

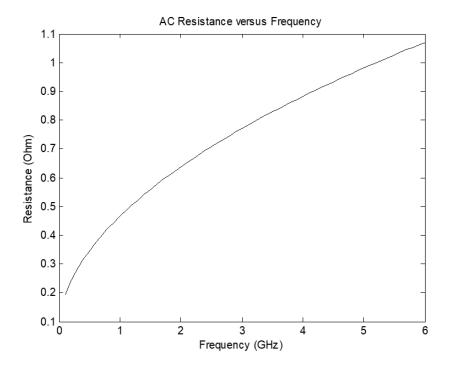

Although the length of the bond wire is short, skin effect at high frequencies increases resistance which can not be ignored. DC series resistance of bond wire can be calculated by using Equation (2.3) [14], where l is the total length, r is the radius of bond wire,  $\sigma$  is the conductivity of the material and t is the thickness of the ground. Because skin effect decreases the conductivity of bond wire by limiting current to the outer conductor surface, resistance calculation should include skin effect. AC resistance of a cylindrical conductor where  $\delta$  is skin depth is given in Equation (2.4) [14].

$$R_{dc} = \frac{l}{\pi \sigma r^2 t} (\pi r^2 + t) \tag{2.3}$$

$$R_{ac} = -\frac{\iota}{\pi \delta \sigma(\delta - 2r)} (2\pi r - \pi \delta + 2) \text{ for } \delta < t \text{ and } \delta < r$$

(2.4)

Total length of the bond wire l can be calculated as given in Equation (2.5).

$$l = \frac{l_1}{\cos(\alpha_1)} + \frac{l_2}{\cos(\alpha_2)} + \frac{l_3}{\cos(\alpha_3)} + \frac{l_4}{\cos(\alpha_4)} + \frac{l_5}{\cos(\alpha_5)}$$

(2.5)

Skin depth formula is given in Equation (2.6) [14].

$$\delta = \sqrt{\frac{1}{\pi \sigma f \,\mu_r \mu_0}} \tag{2.6}$$

Table 2.2: Properties of Bond Wire

| Conductivity of                             | Radius of Bond | Total Length of   | Diameter of     |

|---------------------------------------------|----------------|-------------------|-----------------|

| Gold $(\sigma)$                             | wire $(r)$     | Bond wire ( $l$ ) | Bond wire $(d)$ |

| $4.10 \times 10^7 \left(\frac{s}{m}\right)$ | 12.5 (μm)      | ~1700 (µm)        | 25 (μm)         |

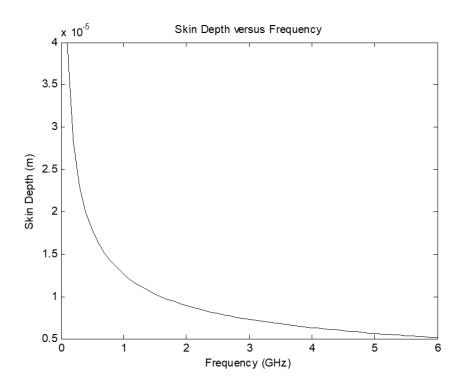

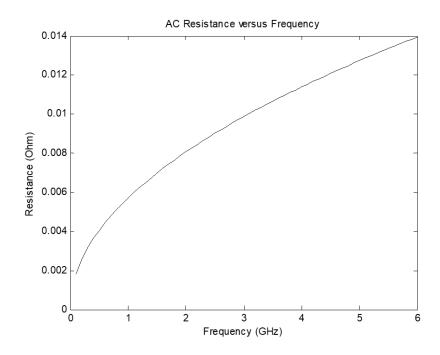

For the bond wire properties given in Table 2.2, skin depth and frequency dependent resistance ( $R_{ac}$ ) values are given in Figure 2.12 and Figure 2.13.

Figure 2.12: Skin Depth versus Frequency Graph of Bond Wire

Figure 2.13: AC Resistance versus Frequency Graph of Bond Wire

Capacitance of the landing pad of the bond wire with the area A on chip can be calculated as given in Equation (2.7) and fringing effect can be ignored [15].

$$C_{pad} = \frac{\varepsilon_0 \varepsilon_r A}{h} \tag{2.7}$$

Capacitive effect on lead side can be neglected because of small area and high distance to ground plane.

Calculated lumped element values of a single bond wire are given in Table 2.3 below.

Table 2.3: Analytically Calculated Lumped Element Values of Single Bond Wire

| Inductance (L) | Pad Capacitance ( $C_{pad}$ ) | Resistance (R)                              |

|----------------|-------------------------------|---------------------------------------------|

| 1.44 nH        | 0.63 fF                       | $R_{ac}$ =Frequency Dependent (Figure 2.13) |

|                |                               | $R_{dc} = 84.5 \ m\Omega$                   |

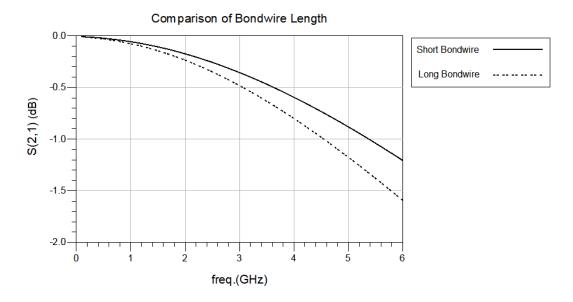

In order to decrease the bond wire inductance, the bond wire profile should be short as much as possible, allowed by manufacturing. Inductances of two different length bond wire profiles are compared in Figure 2.14 . Short one is 1700  $\mu$ m which is used in this work whereas the long one is 2000  $\mu$ m. Inductances of the short and long ones are calculated as 1.44 nH and 1.74 nH, respectively.

Figure 2.14: Comparison of Bond wire Length

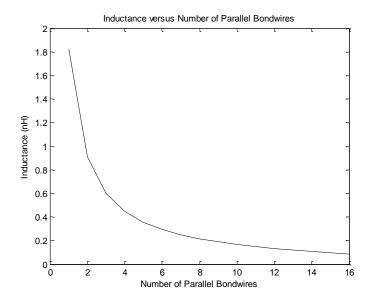

Total inductance of bond wires can be decreased by increasing the number of bond wires which are connected parallel. However, this is not an ultimate solution to the resonance problem as there is not a linear relation between total inductance and the total number of parallel bond wires as seen in Figure 2.15 [15].

Figure 2.15: Inductance versus Number of Parallel Bond Wires

## 2.2.2 Mutual Inductance

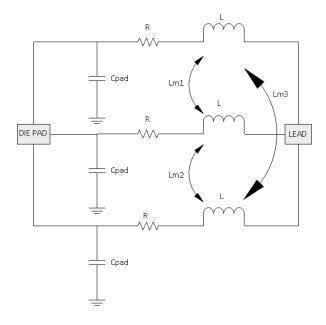

3 parallel bond wires are connected parallel at each gate and drain pads with respect to manufacturing limits. 3 parallel bond wires equivalent model can be represented as Figure 2.16 below.

Figure 2.16: Lumped Element Model of 3 Parallel Bond Wires

Mutual inductance for bond wire pair parallel to ground can be defined as given in Equation (2.8) where d is distance between two bond wires and h is the distance between the ground plane and bond wires [15].

$$L_m = \frac{\mu_r \mu_0}{4\pi} \ln\left(1 + \left(\frac{2h}{d}\right)^2\right) l \tag{2.8}$$

Mutual inductance calculation of first piece of bond wire is given in Equation (2.9)

.

$$L_{im} = \frac{\mu_0}{4\pi} \int_{0}^{l_i \sec{(\alpha_i)}} \ln\left[1 + \left(\frac{2(l\sin(\alpha_i) + h_i)}{d}\right)^2\right] dl \text{ where } i = 1,2,3,4,5$$

(2.9)

Total  $L_{m1}$  and  $L_{m2}$  are calculated as 0.663 nH and  $L_{m3}$  is calculated as 0.446 nH.

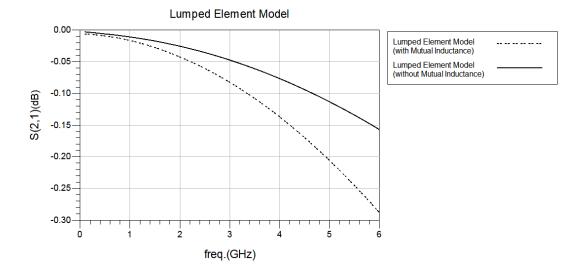

Comparison of 3-parallel bond wires with and without mutual inductances is shown in Figure 2.17. Clearly, the mutual inductance has a significant impact on the overall performance and should be included in the calculations to obtain an accurate model.

Figure 2.17: 3 Parallel Bond Wires with and without Mutual Inductance Model

Because there are 4 gate pads on the gate side and each gate pad includes 3 bond wires, mutual inductance between neighbor bond wires should be calculated and added to the model for a better model accuracy. Hence, 66 mutual inductance values are calculated and added to the model.

### 2.2.3 Lead Model

Gate and drain leads provide connection between PCB and the bare die transistor through bond wires. Capacitance of the package is formed by the lead metals. By decreasing value of lead metal capacitance, resonant frequency can be increased. Reduction of lead capacitance and bond wire inductance creates the same impact in shifting resonant frequency. However, lead metal width should be as large as possible in order to connect parallel bond wires throughout bare die transistor gate and drain pads, without disturbing shapes of them. Similarly shaped bond wires provide same current and power distribution between them which is critical for transistor performance. Also, it should be as narrow as possible to prevent lower resonant frequency of package. In this work, lead metal width is chosen in order to fit in all equally shaped bond wires and prevent decreasing resonant frequency without disturbing manufacturing limits and increasing cost.

Lead can be expressed as microstrip capacitance, inductance and resistance as shown in Figure 2.18.

Figure 2.18: Lead Equivalent Model

Capacitance and inductance calculations are given in Equations (2.10) and (2.11) where w is width of lead, h is distance between ground plane and lead, l is length of lead and c is speed of light in a vacuum [14].

$$C_{lead} = \frac{\varepsilon_r l \left[ \frac{w}{h} + 1.393 + 0.667 \ln \left( \frac{w}{h} + 1.444 \right) \right]}{120\pi c} \text{ for } \frac{w}{h} > 1$$

(2.10)

$$L_{lead} = \frac{120\pi l}{c\left[\frac{W}{h} + 1.393 + 0.667\ln\left(\frac{W}{h} + 1.444\right)\right]} \text{ for } \frac{W}{h} > 1$$

(2.11)

DC resistance of microstrip conductor is calculated as in Equation (2.12) where t is thickness of lead and g is thickness of the ground plane [14].

$$R_{dc} = \frac{l}{\sigma wt} + \frac{l}{\sigma a} \tag{2.12}$$

AC resistance of microstrip conductor is calculated as in Equation (2.13) where  $2\delta < w$ ,  $2\delta < t$  and  $\delta < g$  [14].

$$R_{ac} = \frac{l}{\delta \sigma_0 \sigma_r (2t - 4\delta + 2w)} + \frac{l}{\sigma_0 \sigma_r \delta}$$

(2.13)

By using Equation (2.10)-(2.13), lead capacitance, inductance and resistances are calculated as in Table 2.4. Skin depth and frequency dependent resistance ( $R_{ac}$ ) values are given in Figure 2.19 and Figure 2.20, respectively.

Table 2.4: Analytically Calculated Lumped Element Values of Single Bond Wire

| Inductance $(L_{lead})$ | Capacitance ( $C_{lead}$ ) | Resistance (R)          |

|-------------------------|----------------------------|-------------------------|

| 0.116 nH                | 1.5 pF                     | $R_{ac}$ = Figure 2.20  |

|                         |                            | $R_{dc} = 1.1  m\Omega$ |

Figure 2.19: Skin depth versus Frequency Graph of Lead

Figure 2.20: AC Resistance versus Frequency Graph of Lead

# 2.2.4 Complete Model

By combining the calculated lumped element model of bond wires including mutual inductances and lead capacitances, gate and drain side of the package can be modeled as given in Figure 2.21.

Figure 2.21: Completed Lumped Element Model of Gate or Drain Side of Package

## 2.3 3-D Simulation Model of Package

Final model of the packaged transistor consists of two main parts which are the nonlinear model of the bare die transistor and model of package. The package model cannot be determined by measurement because it is not possible to probe where the bond wires mounted on the chip [5]. Finite Element Method (FEM) is one of the commonly used technique to analyze and characterize geometrically complex 3-D structures such as bond wires and dielectric substrates [5]. 3-D EM simulations are performed by using ADS software in this work.

### 2.3.1 Modeling Strategy

### 2.3.1.1 Material Property Modeling Methodology

### 2.3.1.1.1 Dielectric Loss Models

Dielectric model is extremely important for the overall accuracy of the simulations. The permittivity is a complex number, whose real part  $(\mathcal{E}')$  determines the propagation speed within the dielectric and the imaginary part  $(\mathcal{E}'')$  represents the dielectric losses given in Equation (2.14) [16]. A commonly used term to indicate the dielectric losses is the loss tangent, which is also called as the dissipation factor  $(\tan \theta)$  given in Equation (2.15) [16].

$$\mathcal{E} = \mathcal{E}' - j(\mathcal{E}'') \tag{2.14}$$

$$\tan \theta = \frac{\mathcal{E}''}{\mathcal{E}'} \tag{2.15}$$

The real and imaginary parts of the complex permittivity are related to each other via Kramers-Kronig relations and this should be properly modeled, particularly for broadband simulations. Otherwise, obtained S-parameters may violate causality. In this study, Svensson/Djordjevic model has been adopted, which satisfies the causality requirement [17]. Frequency dependent permittivity formula of Svensson/Djordjevic Model which is used by ADS is given in Equation (2.16) [17].

$$\mathcal{E}(f) = \mathcal{E}_{\infty} + a \cdot \ln \left( \frac{f_H + jf}{f_L + jf} \right) \tag{2.16}$$

$f_H$  and  $f_L$  are low and high frequencies for  $\tan \theta$  calculation respectively.  $\mathcal{E}_{\infty}$  is permittivity value for infinite frequency and a is a constant factor [17].

Although, Svensson/Djordjevic Model is used as the main dielectric loss modeling approach, frequency independent permittivity model gives very similar results in the

frequency domain chosen, because loss tangent  $(\tan \theta)$  values of the dielectric materials of the package are very low. Difference between permittivity values at low and high frequency of operation of transistor is lower than 0.01%.

### 2.3.1.1.2 Impact of Temperature

ADS EM simulator has the capability to define temperature dependent properties of materials. Temperature dependent resistivity and conductivity can be defined for conductors, through Equations (2.17) and (2.18) [17] where  $T_{nom}$  is the nominal temperature,  $T_{C1}$  is linear temperature coefficient and  $T_{C2}$  is quadratic temperature coefficient.

$$R(T) = R(T_{nom}) \times (1 + T_{C1} \times (T - T_{nom}) + T_{C2} \times (T - T_{nom})^{2})$$

(2.17)

$$Cond(T) = \frac{Cond(T_{nom})}{(1 + T_{C1} \times (T - T_{nom}) + T_{C2} \times (T - T_{nom})^2)}$$

(2.18)

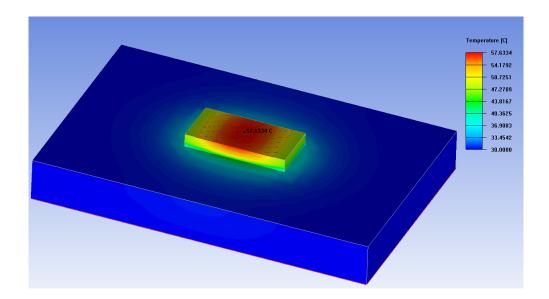

The simulation temperature (T) is defined in the EM simulator setup. Because linear temperature coefficient value of lead and bond wire materials are low and temperature difference between T (approximately 55.5°C as shown in Figure 2.35) and  $T_{nom}$  (25°C) is small, a significant temperature dependence was not observed in the simulations.

### 2.3.1.1.3 Impact of Surface Roughness

Conductors on dielectrics do not have perfectly smooth surface [17]. Copper surface roughness increases conductor loss and slows the phase velocity of signals. Losses due to copper surface roughness depends on frequency and increases with increasing frequency. Loss becomes significant when skin depth is comparable or lower than surface roughness. Typical surface roughness values are in the range of  $0.5-6~\mu m$ .

Skin depth of copper at 1 GHz is around 2 µm. Thus, surface roughness is significant for multi-gigahertz signal components [18].

Three models are available in ADS EM simulator which are the Hammerstead, the Hemispherical model and the Huray models. Roughness data which is provided by manufacturer is enough to calculate the surface roughness but for more accuracy, other parameters should be obtained by scanning electron microscope (SEM) [17]. The simulator determines the parameter values even if they are not described by using the roughness data. The Hammerstad model is not accurate at high frequencies. The hemispherical model is more accurate than the Hammerstad model, but it still losses accuracy at high frequencies. The Huray model provides good accuracy for frequencies over 50 GHz [17].

Since the operating frequencies of the transistor are quite low and surface roughness of conductor materials are quiet low with respect to skin depth, the impact of surface roughness on conductor loss is negligible.

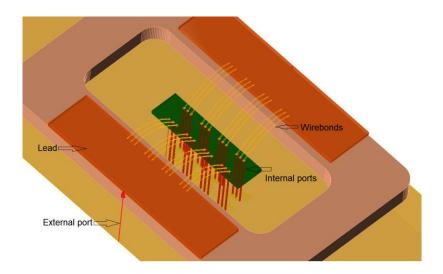

## 2.3.1.2 3-D EM Modeling Methodology

Because only the passive part of the package is needed to be analyzed, active part which is the bare die transistor should be removed without affecting the electromagnetic behaviour [6]. Thus, bare die transistor is replaced by a GaN dielectric block. On the top of this dielectric block, metal areas are placed which represent the gate and drain pads of bare die transistor. Internal ports are placed at the end of bond wires on metals. For each bond wire, one internal port is defined. Because die transistor is removed and there is no connection between gate and drain pads on GaN dielectric block, there is no transmission between external ports. Thus, resonant frequency of package can be obtained by performing small signal analysis.

External ports are placed at the edge of the gate and drain leads of the package. As a result of full-wave EM simulation, a multi-port S-parameter matrix is obtained. By inserting the nonlinear model of the bare die transistor to the internal ports on GaN dielectric block, model of packaged transistor is obtained.

# 2.3.2 Layout

Another integral part of the modeling process is the layout generation which is composed of defining the bond wire profile and stack-up.

#### 2.3.2.1 Bond Wire Profile

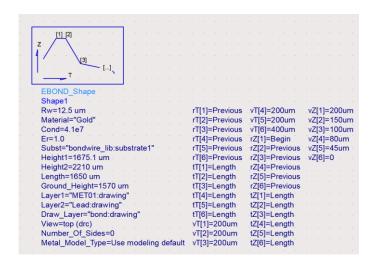

EBOND shape component is a bond wire profile generation tool used in ADS. By using parameter window shown in Figure 2.22 below, all the values which determine the shape of a bond wire can be specified.

Figure 2.22: EBOND Shape Component

Standard EBOND shape parameters such as radius, material, height, length etc. can be defined within this window. Substrate is selected as initialization for the height settings for circuit simulation. Shape of the bond wire is created as seen in Figure 2.23 by introducing length and height of pieces.

Figure 2.23: EBOND Shape Parameter Window

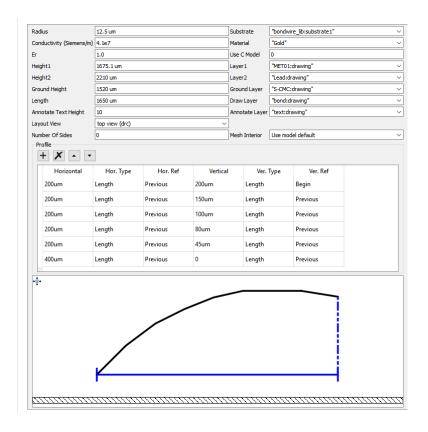

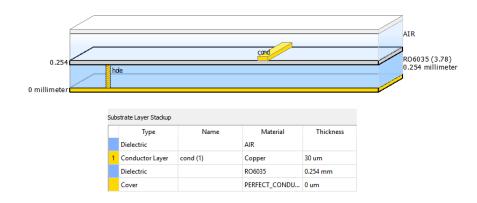

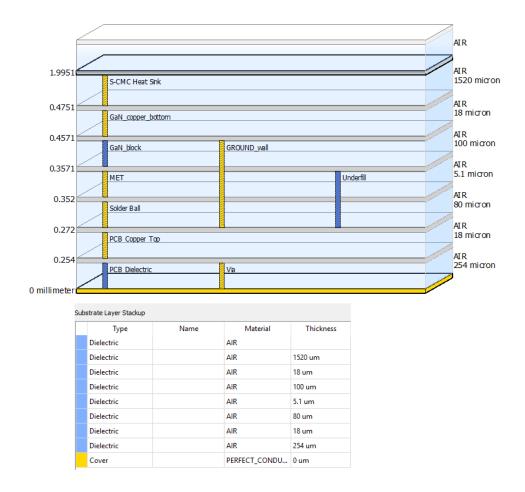

## 2.3.2.2 Defining Stack-up

A well defined stack-up is required in order to simulate a design. Stack-up definition consists of various layers of metal, dielectric material and ground planes. Also, position of layers of physical design in the substrate and specifications of material characteristics are included. Stack-up is created as a first step of 3-D EM simulation as seen in Figure 2.24.

Figure 2.24: Stack-up of Package

# 2.3.2.3 Assigning Ports

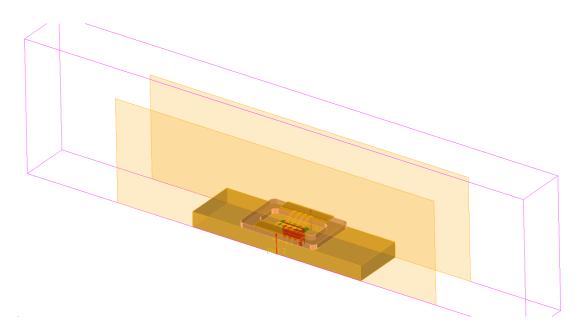

3-D layout is created as shown in Figure 2.25. Ports are necessary in order to inject energy into circuit to analyze the circuit behavior [6].

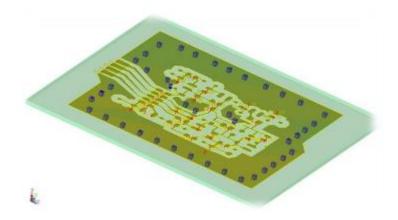

Figure 2.25: Lay-out of 3-D Package

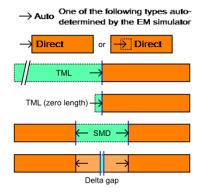

Lay-out pins are used to define ports in ADS which are point pin, area pin and edge pin [19]. Point pin can be used inside a metal which defines cylinder port. Area pin is used inside a metal which defines cylinder port too. Edge pin can be used at the edge of a metal which defines sheet port or waveguide port as seen in Figure 2.26 [19].

Figure 2.26: Pin and Port Relation for EM Simulations in ADS [19]

Edge pins are assigned at the edge of gate and drain leads. Feed type of external ports is chosen as TML which is defined as 'Waveguide Port' and can be applied to surface of bounding box. TML calibration assumes the structure is fed through a transmission line [19]. TML calibration removes the parasitic effects and fringe capacitance at the edge of the metal. Modal TML port solver is used to excite structure by using TML port. The modal S-parameters obtained may not be stable at low frequencies, although being more accurate at high frequencies [19]. Generalized S-parameters with reference impedance that is frequency dependent characteristic impedance for each modes can be described as modal S-parameters, which are useful to analyze transitions between microstrip lines with different impedances. External ports can be seen in Figure 2.27.

Figure 2.27: External Ports

Point pins are assigned at the end point of each bond wire which can be defined as 'Cylinder Port' which use cylindrical set of current filaments as shown in Figure 2.28. Direct port is used when circuit includes transmission lines that connect to a device such as a transistor. [19]. Because direct port is partially calibrated, it removes self and mutual inductance between ports.

Figure 2.28: Internal Ports

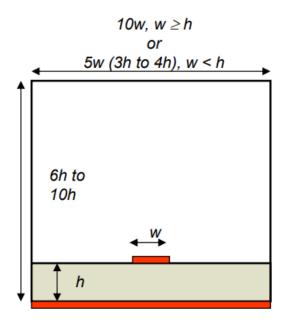

To analyze the sturucture accurately, modal excitations, modal impedances and propagation should be solved correctly [20]. If port width is chosen too narrow, fields can couple to side walls and incorrect modal solution is obtained. Also, if port length is chosen too short, fields can couple to the top wall. Thus, size of waveguide port can be adjusted by using the guideline in Figure 2.29 [20]. If width of the microstrip trace, w, is more than the dielectric height, h, the width of the port should be chosen as  $10 \ w$ . The height of the port can be chosen between  $6 \ h$  and  $10 \ h$ . In this work, the width of the port is chosen as  $8 \ h$ .

Figure 2.29: Waveguide Port Dimension Guideline [20]

Because FEM ports are physical models and physically meshed, they have self-inductance [21]. Also, there is mutual inductance between uncalibrated ports. Feed type determines calibration of ports. The FEM feed types used in ADS and which effect is calibrated out is described in Table 2.5 [21].

Table 2.5: Feed Type versus Calibration used in ADS [21]

| Feed Type             | Removes Self-Inductance | Removes Mutual Inductances  |

|-----------------------|-------------------------|-----------------------------|

| Auto, TML, TML        | Yes                     | Yes                         |

| (zero length), Direct |                         |                             |

| SMD                   | Yes                     | Not with other SMD or Delta |

|                       |                         | Gap ports                   |

| Delta Gap             | No                      | Not with other SMD or Delta |

|                       |                         | Gap ports                   |

### 2.3.3 Simulation

Finite element method (FEM) simulation technique is used in order to calculate 3-D EM field inside an arbitrarily shaped passive 3-D structure [19]. FEM divides the full space of problem into smaller regions which are called as tetrahedras and by using local function field in each tetrahedras is represented [19]. To increase accuracy of simulation results, FEM mesh settings should be made carefully. There is a trade-off between mesh size and computer memory and process time. To produce appropriate mesh structure, the iterative process is used. Mesh is refined in critical regions automatically in this process. It generates a solution and refines the mesh with respect to delta error and creates better solution until S-parameters converge to the desired limit. Also, maximum number of adaptive passes should be determined, which is the number of refinement passes reached before the delta error criterium is met and refinement process ends. Refinement frequency should be determined to specify the frequency where mesh will be generated. The refinement frequency is chosen as 12 GHz, because current distribution should be investigated at the highest simulation frequency to prevent missing spatial variations in reality [19]. After defining mesh settings, solver settings should be defined. Iterative process is chosen, because memory requirements and computing time is lower than the direct solver which guarantee convergence. However, by chosing maximum number of iterations sufficiently, convergence of solutions can be improved.

In this work, simulation frequency range for FEM simulation is set up to 12 GHz. Although operating frequency band of packaged transistor is DC to 4 GHz, to include 2<sup>nd</sup> and 3<sup>rd</sup> harmonic behaviour, simulation frequency bandwidth is chosen over wideband.

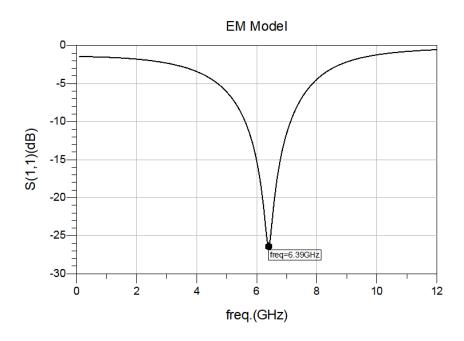

Resonant frequency of simulated package is around 6.39 GHz as seen in Figure 2.30 below. This means that above approximately 4 GHz, package decreases performance of transistor dramatically.

Figure 2.30: Resonance of the Input Circuit of Package in S<sub>11</sub>

## 2.4 Comparison of Models

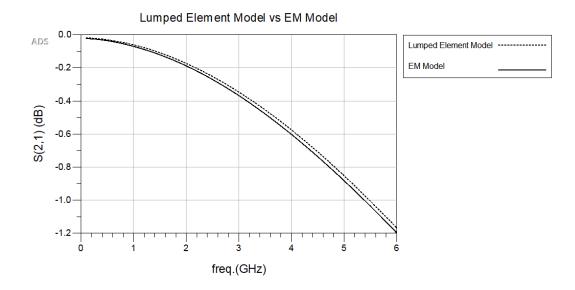

Comparison of calculated lumped element model of single bond wire and EM analysis of it are shown below in Figure 2.31. Thus, there is no significant difference between models of single bond wires.

Figure 2.31: EM Model versus Lumped Element Model S<sub>21</sub> Graph of Single Bond wire Model

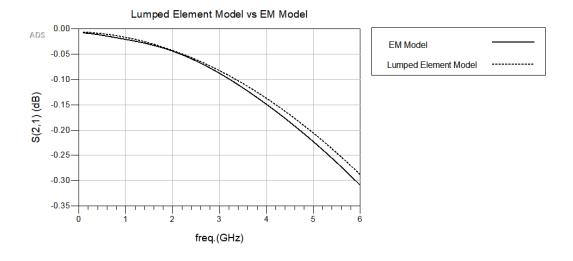

Also, comparison of calculated lumped element model of 3 parallel bond wires and EM analysis of them is shown below in Figure 2.32. Thus, there is no significant difference between models of three parallel bond wires.

Figure 2.32: EM Model versus Lumped Element Model S<sub>21</sub> Graph of Three Parallel Bond wire with Mutual Inductance Between Bond wires

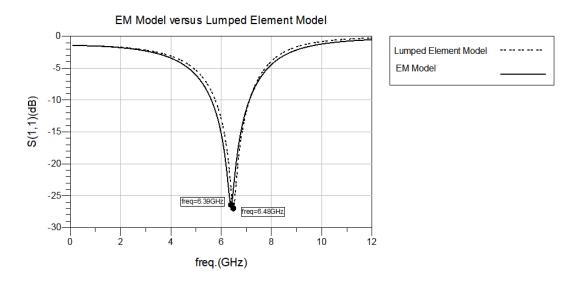

Resonant frequencies of the EM and lumped element models of the package are around 6.39 GHz and 6.48 GHz, respectively as seen in Figure 2.33.

Figure 2.33: EM Model versus Completed Lumped Element Model of Package S<sub>11</sub> Graph

This comparison shows that both EM model and lumped element model can be used accurately for this package. EM model is generally more accurate than lumped element model because geometrically complex structures can be characterized in electromagnetic environment and all effects can be added to the calculations with FEM analysis. The parasitic effect between gate and drain bond wires, coupling between the input and the output of the package or other effects between materials can not be predicted by using analytical calculations. If the frequency band of operation of transistor is higher, these parasitic effects get more important. In this work, the operating frequency of the transistor is quite low, thus lumped element model can predict accurate results.

The other important difference between the lumped element and the EM model is the need for sophisticated simulation software. If lumped element model is chosen, basic equations can be derived from the bond wire geometry and analytical calculations are sufficient to create a model. On the other hand, to create an EM model, more complex and long time process is needed. Creating wirebond profile, defining substrate and assigning ports should be performed carefully to solve the problem accurately. Because the structure is complex, simulation takes long time as well.

## 2.5 Thermal Characterization of Air Cavity Ceramic Package

In addition to the electrical performance, thermal resistance of packages is another important design parameter. Thermal resistance is an ability of package to transfer the heat, which is generated by the transistor die, to the ambient. In order to obtain high performance air cavity ceramic package transistor, heat transfer should be through cold plate which is attached to the base of the package. Junction temperature refers to the temperature of chip transistor and case temperature refers to the temperature of the outside surface of the package which is at the center of the S-CMC block. In order to calculate the thermal resistance, Equation (2.19) [22] can be used where L is width (m), k is thermal conductivity  $\left(\frac{W}{m.K}\right)$  and A is area  $(m^2)$  of the surface to which the heat will be transfered.

$$R = \frac{L}{kA} \tag{2.19}$$

In order to calculate temperature difference between cold plate and case, Equation (2.20) [22] can be used where Q is dissipated power (W), R is thermal resistivity  $\left(\frac{{}^{\circ}C}{W}\right)$  and  $\Delta T$  is temperature difference ( ${}^{\circ}C$ ).

$$\Delta T = QR \tag{2.20}$$

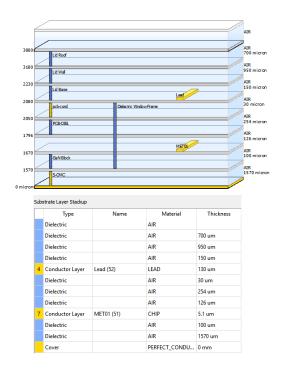

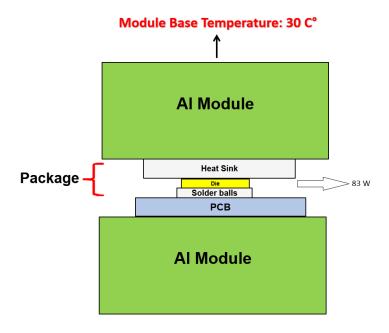

# 2.5.1 Thermal Model Description

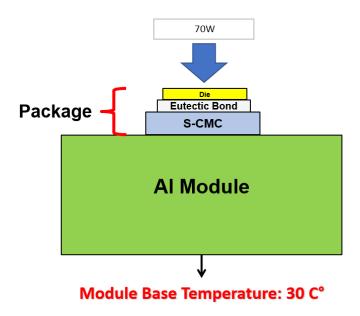

A die transistor is soldered to the top of the S-CMC block. S-CMC block is attached to the Al Module with screws. Module base temperature remains stable at 30 °C. Thermal model stack-up is prepared as seen in Figure 2.34. Thermal properties of materials and their dimensions are referred in Table 2.6.

Figure 2.34: Air Cavity Ceramic Package Thermal Stack-Up

Table 2.6: Material Properties of Package

| Layer     | Material  | Dimension             | Thickness             | Thermal Conductivity         |

|-----------|-----------|-----------------------|-----------------------|------------------------------|

|           |           | $(m^2)$               | ( <i>m</i> )          | $\left(\frac{W}{m.K}\right)$ |

| Al Module | Aluminum  | 1.04×10 <sup>-3</sup> | 5.00×10 <sup>-3</sup> | 180.00                       |

| S-CMC     | Composite | $8.58 \times 10^{-5}$ | $1.57 \times 10^{-3}$ | 301.80                       |

# 2.5.2 Calculation and Simulation Comparison

In order to perform thermal analysis, large signal test result of the amplifier which is designed by using the air cavity ceramic package model is needed. Large signal test result of designed PA is shown in Table A. Maximum dissipated power which is spread as heat to the ambient is 70 W.

Thermal resistances of layers which should be verified by simulation are calculated in Table 2.7.

Table 2.7: Thermal Resistance of Layers

| Layer    | Dimension             | Thickness             | Resistance                           | Temperature |

|----------|-----------------------|-----------------------|--------------------------------------|-------------|

|          | $(m^2)$               | ( <i>m</i> )          | $\left(\frac{{}^{\circ}C}{W}\right)$ | (°C)        |

| Al Modul | 1.04×10 <sup>-3</sup> | $5.00 \times 10^{-3}$ | 2.67×10 <sup>-2</sup>                | 31.87       |

| S-CMC    | 8.58×10 <sup>-5</sup> | 1.57×10 <sup>-3</sup> | 0.6×10 <sup>-1</sup>                 | 36.07       |

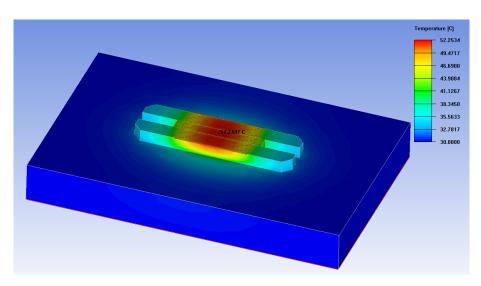

To create thermal model of the air cavity ceramic package and simulate thermal characteristics of it, HFSS-ICEPACK program is used.

Figure 2.35: Simulation Result of Package

As seen in Figure 2.35, case temperature is calculated by the software as 52.25 °C which is not close to the calculated temperature of 36.07 °C as given in Table 2.7. Because the area of the die transistor is far smaller than the area of S-CMC flange, heat spread through the flange is nonuniform. Thus, it can be said that equations are